# **Doctoral Thesis**

## Thesis Title

# Studies on Graphene Field Effect Transistors: Solution-Processed Gate Dielectrics and UV-Ozone-Processed Contact Resistance

Department of Electronic Engineering

Graduate School of Engineering,

TOHOKU UNIVERSITY

Goon-Ho Park

(ID No. B1TD9210)

#### **Doctoral Dissertation**

# submitted in partial fulfillment of the requirements for the degree of

## **DOCTOR of ENGINEERING**

in the Department of Electronic Engineering,

Graduate School of Engineering

TOHOKU UNIVERSITY

#### Goon-Ho Park

Thesis Committee: Professor Maki Suemitsu, Chair

Professor Shigeo Sato

Professor Taiichi Otsuji

Associate Professor Tetsuya Suemitsu

Associate Professor Hirokazu Fukidome

# **Studies on Graphene Field Effect Transistors:**

## **Solution-Processed Gate Dielectrics and**

### **UV-Ozone-Processed Contact Resistance**

#### Goon-Ho Park

#### **Abstract**

Graphene has been attracting considerable interest for various applications such as transparent electrodes, sensors, solar cells, and transistors due its outstanding electrical, optical and mechanical properties. A number of researchers have especially focused on developing graphene field-effect transistors (GFETs) to replace conventional silicon-based devices. Many challenges however still remain to be overcome. This research, aimed at developing high performance GFETs, is focused on improving the process design and the device structure of GFETs to fully extract graphene's excellent properties.

First, a novel gate dielectric deposition method has been developed based on a solution process. The process parameters are tuned to minimize the doping, strain, defect density in graphene during the gate dielectric deposition. As a result, a modified solution process is proposed, which consists of formation of an initial ultrathin Al<sub>2</sub>O<sub>3</sub> seeding layer, spin-coating, oxygen-plasma treatment, post-deposition annealing (PDA). A high intrinsic carrier mobility of 8400 cm<sup>2</sup>/Vs was obtained by minimizing the doping, strain and defects to graphene in top-gated GFETs.

Second, UVO<sub>3</sub> treatment during the contact electrode formation as well as fabrication of overlapped S/D to top-gate device are proposed to reduce the series resistance: the access and the contact resistance. As a result, low contact resistances, comparable to one of the best reported values, were achieved due to effective removal of interfacial contaminations and reduction of the access length.

Finally, a top-gated GFET, consisting of modified solution-processed gate dielectrics, UVO<sub>3</sub>-treated contacts, and overlapped S/D to gate structure, was fabricated and characterized. As a result, a highest transconductance of 358  $\mu$ S and a field-effect mobility of 301 cm<sup>2</sup>/Vs, not achievable by either the solution-gate or the UVO<sub>3</sub> treated contacts alone, have been obtained. These high transconductance and the field-effect mobility values are attributed to both increase of the intrinsic mobility and reduction of the contact resistance. The intrinsic mobilities were actually as high as 8620 cm<sup>2</sup>/Vs for holes and 8650 cm<sup>2</sup>/Vs for electrons. A low contact resistance of 900  $\Omega$  $\mu$ m was obtained. The combination of the solution-processed gate dielectric, UVO<sub>3</sub>-treated contacts, and overlapped S/D to gate structure is quite promising for high performance GFETs.

# **CONTENTS**

| Chapter | 1 Introduction                                    | . 1 |

|---------|---------------------------------------------------|-----|

| 1.1     | Limitation of MOSFET Scaling                      | . 1 |

| 1.2     | Graphene as an Alternative Material               | . 3 |

|         | 1.2.1 Structural Properties of Graphene           | . 3 |

|         | 1.2.2 Electrical Properties of Graphene           | . 5 |

| 1.3     | Graphene FET applications                         | . 8 |

|         | 1.3.1 GFETs for logic applications                | . 9 |

|         | 1.3.2 GFETs for RF applications                   | 11  |

| 1.4     | Cheallenges on GFETs                              | 13  |

| 1.5     | Outline                                           | 15  |

| Refe    | erence                                            | 17  |

| Chapter | 2 Solution-processed gate dielectrics for GFETs   | 20  |

| 2.1     | Introduction                                      | 20  |

| 2.2     | Raman evaluation of doping and strain in graphene | 22  |

|         | 2.2.1 Principle of Raman scattering spectroscopy  | 22  |

|         | 2.2.2 Raman spectrum of graphene                  | 24  |

|         | 2.2.3 Raman spectrum in doped graphene.           | 28  |

|     |      | 2.2.4 Raman spectrum in strained graphene                                 | . 30 |

|-----|------|---------------------------------------------------------------------------|------|

|     |      | 2.2.5 Separation of the impacts from charge doping and strain in graphene | . 31 |

|     | 2.3  | Device fabrication                                                        | . 34 |

|     | 2.4  | Results and Discussion.                                                   | . 36 |

|     | 2.5  | Conclusion                                                                | . 46 |

|     | Refe | erence                                                                    | . 47 |

| Cha | pter | 3 Electrical properties of GFETs with solution-processed top-gate         | . 50 |

|     | 3.1  | Introduction                                                              | . 50 |

|     | 3.2  | Definition of intrinsic mobility in GFETs                                 | . 53 |

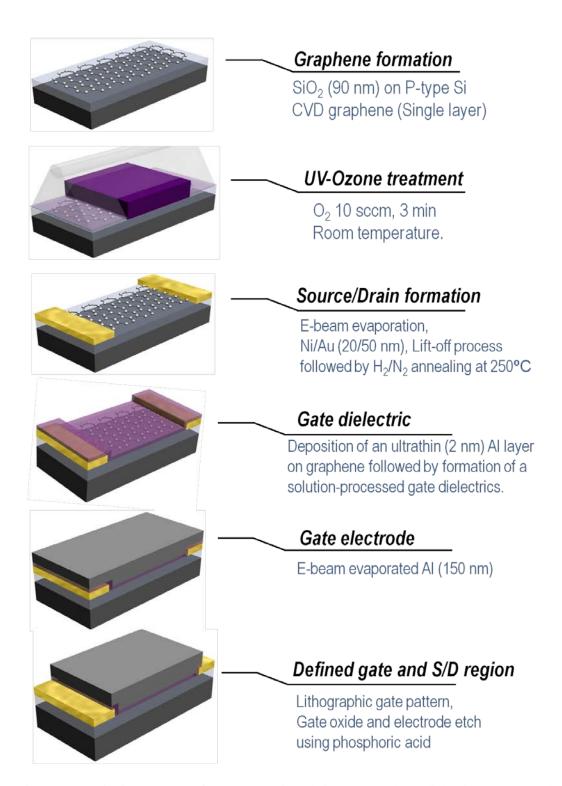

|     | 3.3  | Device fabrication                                                        | . 54 |

|     | 3.4  | Results and Discussion.                                                   | . 56 |

|     | 3.5  | Conclusion                                                                | . 64 |

|     | Refe | erence                                                                    | . 65 |

| Cha | pter | 4 UV-Ozone-processed contacts for GFETs                                   | . 67 |

|     | 4.1  | Introduction                                                              | . 67 |

|     | 4.2  | Device Fabrication                                                        | . 69 |

|     | 4.3  | Result and Discussion                                                     | . 71 |

|     |      | 4.3.1 Surface morphology and defects to graphene                          | . 71 |

|     |      | 4.3.2 Electrical characteristics                                          | . 74 |

|     |      | 4.3.3 Extraction of contact resistance                                    | . 77 |

|     | 11   | Conclusion                                                                | ۷1   |

| Refe      | rence 8                                                                          | 2 |  |

|-----------|----------------------------------------------------------------------------------|---|--|

| Chapter   | 5 Electrical properties of GFETs with a overlapped S/D to top-gate and UV-Ozone- |   |  |

| processed | l contacts                                                                       | 4 |  |

| 5.1       | Introduction                                                                     | 4 |  |

| 5.2       | Device Fabrication                                                               | 7 |  |

| 5.3       | Result and Discussion                                                            | 9 |  |

| 5.4       | Conclusion 9                                                                     | 7 |  |

| Refe      | rence 9                                                                          | 8 |  |

| Chapter   | 6 GFETs with solution-processed top gate and UV-Ozone-processed contacts         | 9 |  |

| 6.1       | Introduction 9                                                                   | 9 |  |

| 6.2       | Device Fabrication                                                               | 1 |  |

| 6.3       | Result and Discussion                                                            | 3 |  |

| 6.4       | Conclusion                                                                       | 7 |  |

| Refe      | rence                                                                            | 8 |  |

| Chapter   | 7 Conclusion                                                                     | 9 |  |

| Publicati | ons and Conference Proceedings                                                   | 2 |  |

| Acknowl   | Acknowledgements                                                                 |   |  |

# **List of Figures**

- Figure 1.1. (a) Atomic structure of graphene, (b)  $\pi$  (blue) and  $\sigma$ -bonds (yellow) in graphene.

- Figure 1.2. Lattice structure of graphene with basis of two atoms denoted as A and B.

- Figure 1.3. Band structure of graphene.

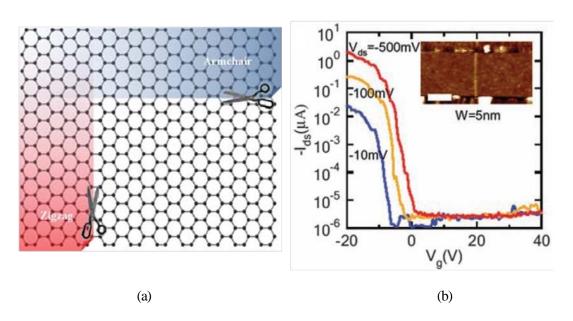

- Figure 1.4. (a) Schematic of cutting the graphene sheet to obtain zigzag and armchair GNR (b)

Transfer characteristics for a width of 5 nm and channel length of 130 nm GNR with Pd contacts and Si backgate.

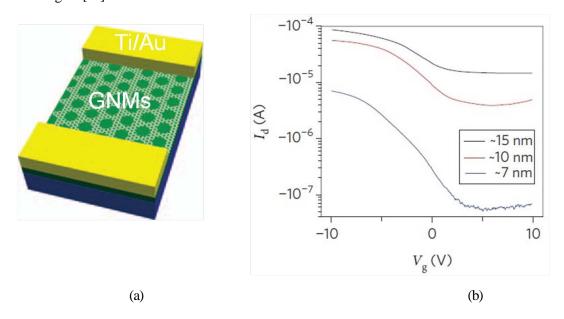

- Figure 1.5. (a) Schematic of GNM-FET (b) Transfer characteristics for GNMs with different estimated neck width of 15, 10 and 7 nm.

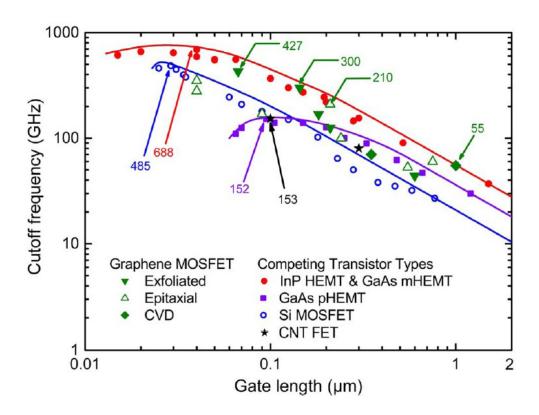

- Figure 1.6. Comparison of cut off frequency between GFET and other devices, as a function of gate length  $L_{\rm G}$ .

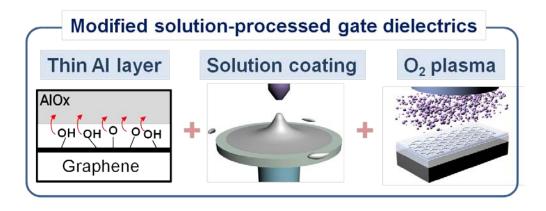

- Figure 2.1. Composition of modified solution-processed gate dielectrics.

- Figure 2.2. Quantum energy transitions for Rayleigh and Raman scattering.

- Figure 2.3. Raman spectrum of graphite and monolayer graphene.

- Figure 2.4. (a) G band vibration modes for the iTO (in-plane transverse optical) phonons at the  $\Gamma$ point (b) First-order Raman scattering process.

- Figure 2.5. (a) Second-order Raman scattering process (b) D band  $A_1$ ' vibration mode for the iTO phonon at the K-point.

- Figure 2.6. (a) Electronic structure of graphene: (up) undoped graphene (down) p-type doped graphene (b) G band energy (squares) and G band width (circles) as function of gate voltage and charge density.

- Figure 2.7. (a) Bands of perfect crystal; Bands in the presence of an  $E_{2g}$  lattice distortion within (b) ABO (c) non-adiabatic (d) Atomic pattern of the  $E_{2g}$  phonon.

- Figure 2.8. (a) Deformation of graphene on  $SiO_2$  (b) Graphene lattice structure deformed by strain (c) D, G, 2D (G') peaks plotted as a function of the biaxial strain  $\varepsilon_{\parallel}$ .

- Figure 2.9. (a) Correlation between the frequencies of the G and G' (2D) Raman modes of graphene. (b) The theoretical and experimental trajectories of  $(\omega_G, \ \omega_G)$  affected by hole concentration and strain.

- Figure 2.10. Fabrication sequences of dielectric formation on graphene and MIM capacitor.

- Figure 2.11. Thickness of solution-processed gate dielectrics formed at 250  $^{\circ}$ C PDA as a function of Al<sub>2</sub>O<sub>3</sub> solution/thinner ratios.

- Figure 2.12. *C-V* characteristics of solution-processed gate dielectrics (a) without and (b) with oxygen plasma treatment.

- Figure 2.13. (a) Dielectric constant, as determined from *C-V* measurement, of the Al<sub>2</sub>O<sub>3</sub> film with (solid squares) and without (open squares) oxygen plasma treatments as a function of the PDA temperature and time. (b) *J-V* characteristics of the Al<sub>2</sub>O<sub>3</sub> MIM capacitor with oxygen plasma treatment.

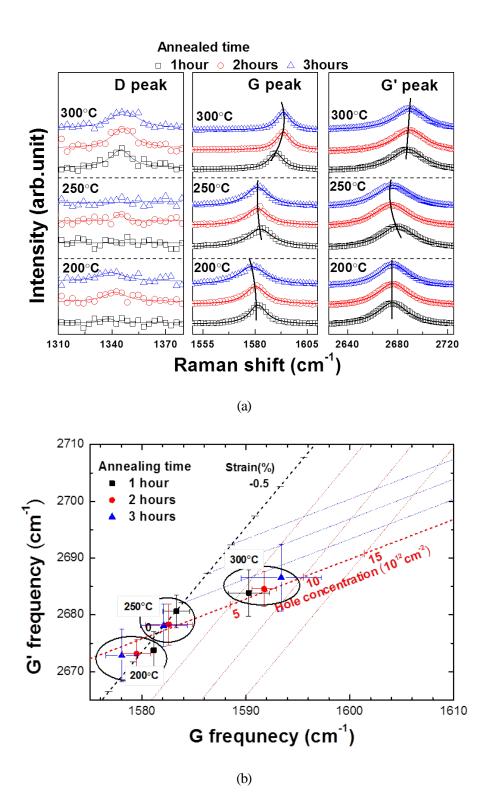

- Figure 2.14. (a) Raman spectrum of oxygen-plasma-treated films as a function of the PDA temperature and (b) G' peak position versus G peak position of the films with (solid squares) and without (open squares) oxygen plasma treatment for several PDA temperatures.

- Figure 2.15. (a) Raman spectrum of  $Al_2O_3$  on graphene with initial insertion of natural oxide of Al. (b) G' peak position versus G peak position as a function of the PDA temperature and time for  $Al_2O_3$  on graphene with initial insertion of thin Al layer and with oxygen plasma

treatment.

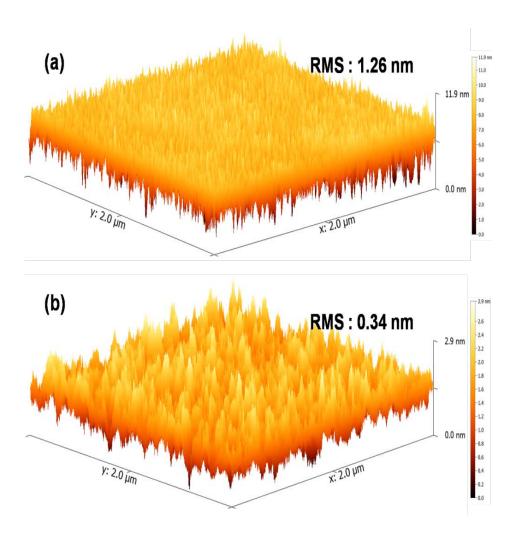

- Figure 2.16. AFM images of (a) Al (2 nm) deposited film on graphene and of (b) solution-processed  $Al_2O_3$  film on Al (2 nm) with oxygen plasma and PDA at 250 °C.

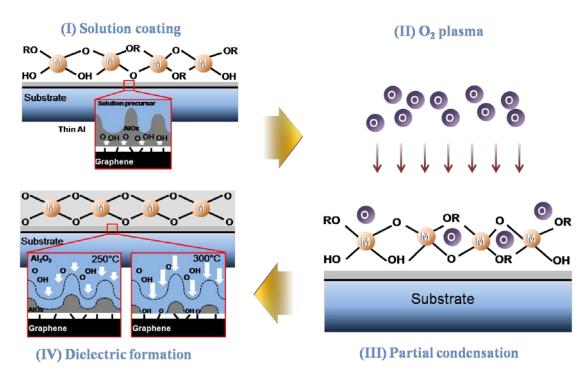

- Figure 2.17. Schematic of the mechanism for the oxygen plasma growth for solution-processed Al<sub>2</sub>O<sub>3</sub>.

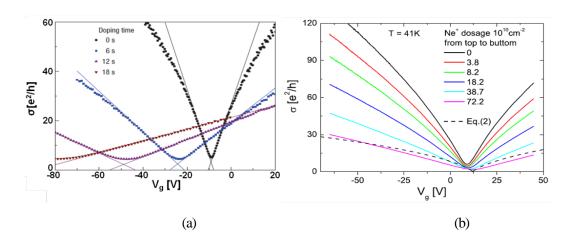

- Figure 3.1. Conductivity versus gate voltage curves for (a) the pristine sample and three different doping concentrations (b) pristine graphene and following Ne<sup>+</sup> ion irradiation doses with cumulative exposures indicated.

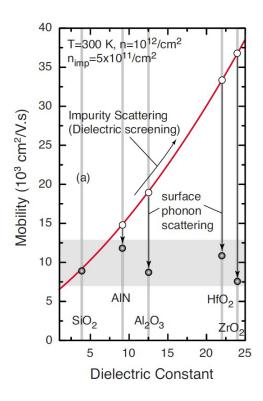

- Figure 3.2. Carrier mobilities in graphene as a function of gate dielectric constant.

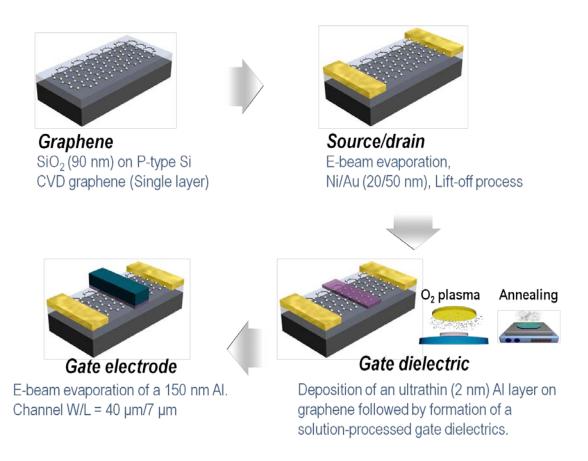

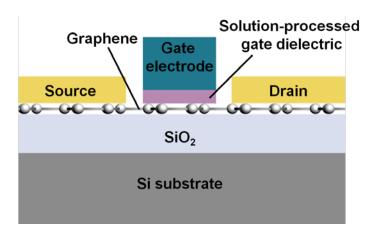

- Figure 3.3. Fabrication flow of TG-GFET with solution-processed gate dielectric.

- Figure 3.4. Schematic diagram of the TG-GFET with solution-processed gate dielectric.

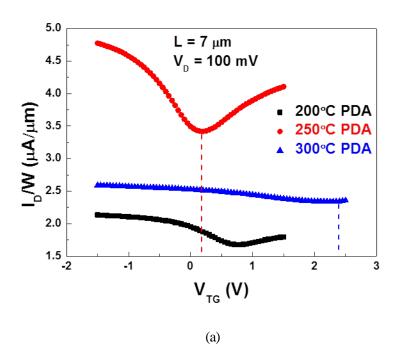

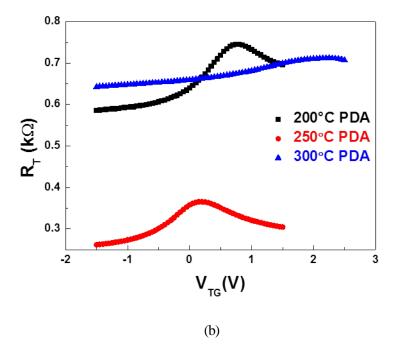

- Figure 3.5. (a) Transfer characteristics of the drain current as a function of the gate voltage  $(I_D V_G)$  with various PDA temperatures. (b) Total resistance as a function of the gate voltage  $(R_T V_G)$  with various PDA temperatures.

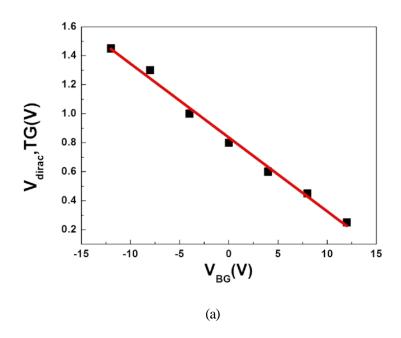

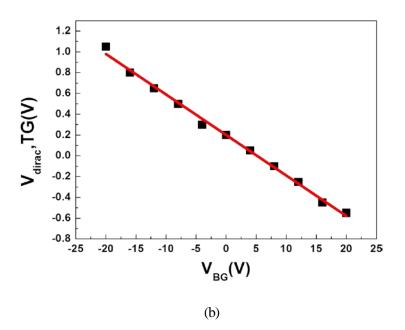

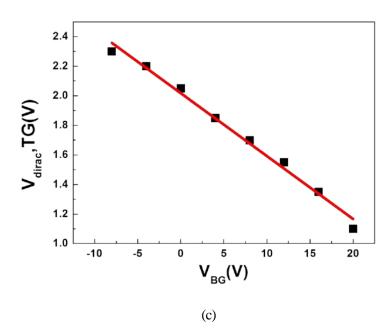

- Figure 3.6. Dirac voltage as a function of the  $V_{BG}$  of TG-GFETs with solution-processed gate dielectric annealed (a) at 200 °C (c) at 250 °C (e) at 300 °C.

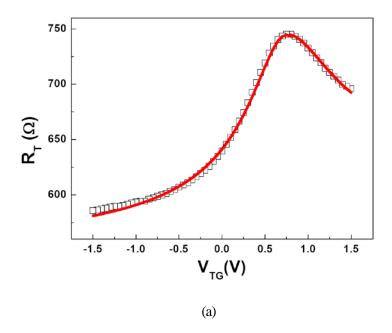

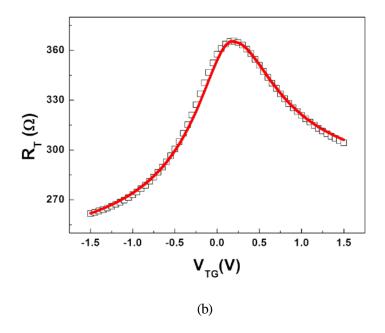

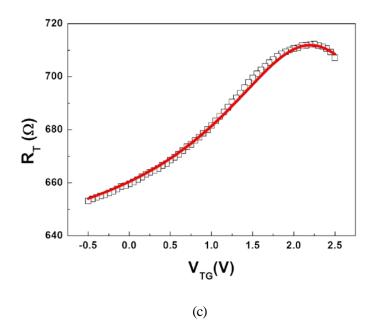

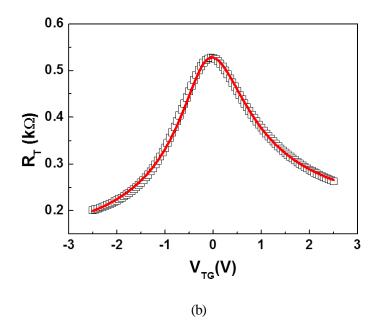

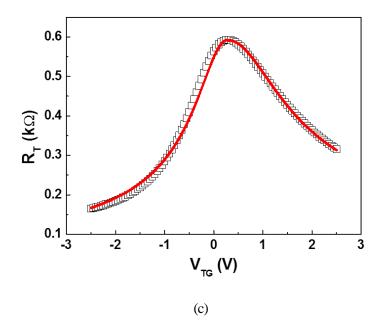

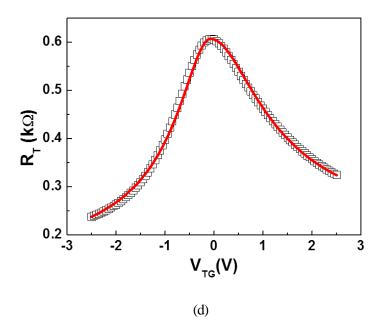

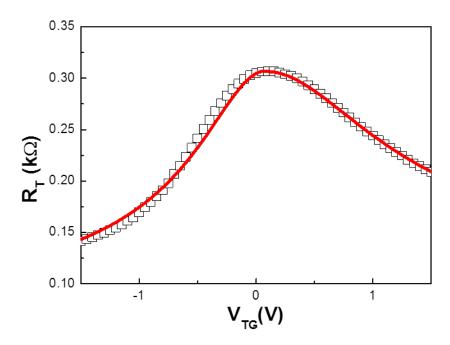

- Figure 3.7. Measured  $R_T$  versus  $V_G$  (black square) of TG-GFETs with solution-processed gate dielectric annealed (a) at 200 °C (b) at 250 °C (c) at 300 °C and fitted result (red line) with equation, respectively.

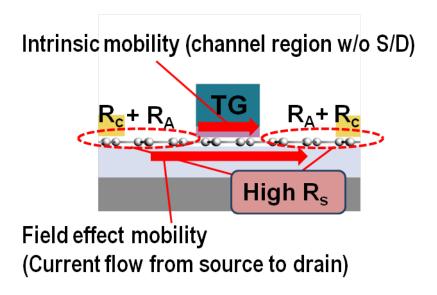

- Figure 3.8. Comparison between intrinsic mobility and filed effect mobility.

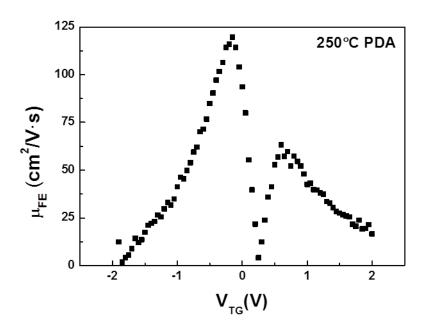

- Figure 3.9. Field effect mobilities of TG-GFETs with solution-processed gate dielectric formed at 250°C.

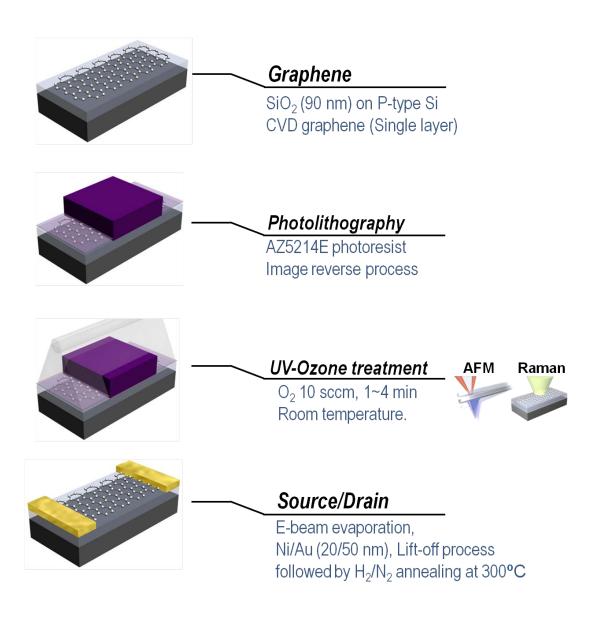

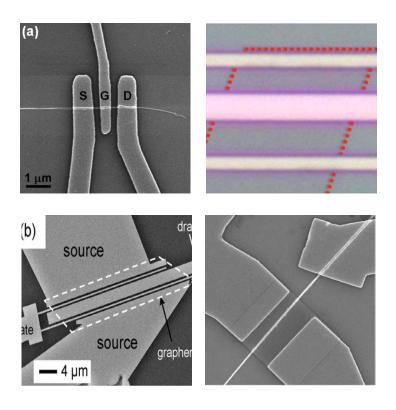

- Figure 4.1. Fabrication sequences of BG-GFETs with UVO<sub>3</sub> treated contact.

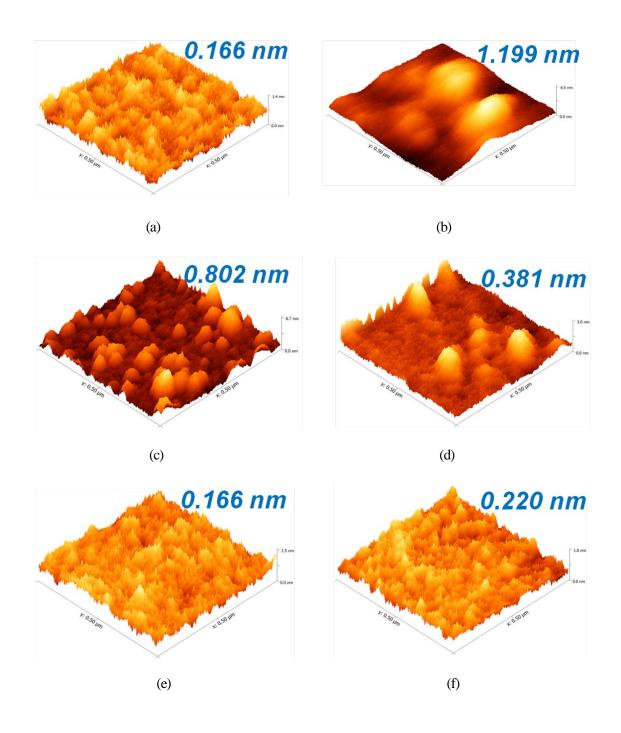

- Figure 4.2. Surface morphology on graphene, measured by AFM, (a) in pristine graphene (b) after

- photolithography (c) UVO<sub>3</sub> for 1 min (d) UVO<sub>3</sub> for 2 min (e) UVO<sub>3</sub> for 3 min (f) UVO<sub>3</sub> for 4 min.

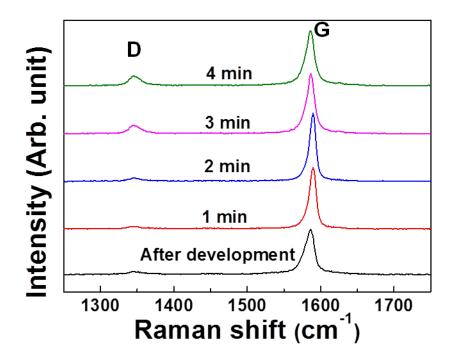

- Figure 4.3. Raman spectrum of D and G peak before and after UVO<sub>3</sub> treatment.

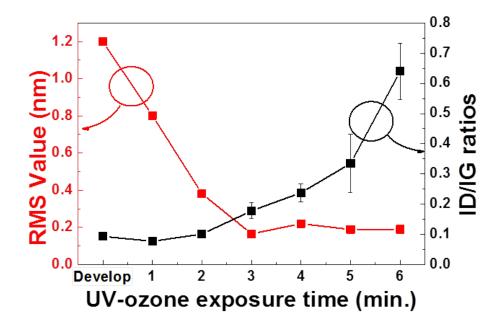

- Figure 4.4. RMS value and  $I_D/I_G$  ratios, determined by AFM and Raman scattering spectroscopy, respectively, as a function of UVO<sub>3</sub> treated time.

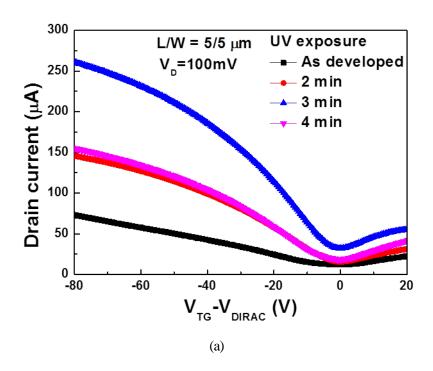

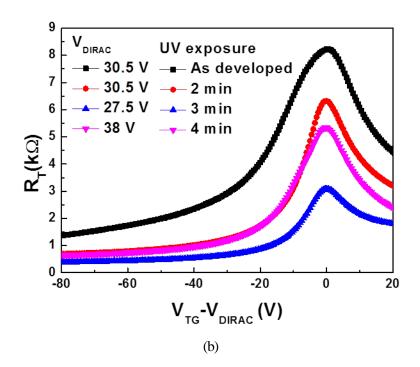

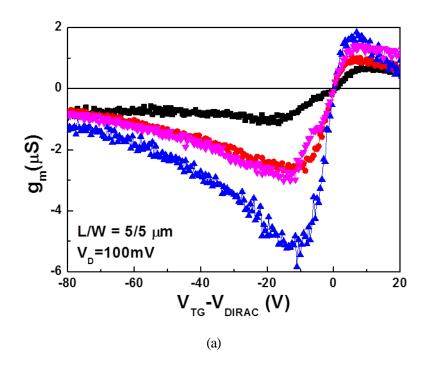

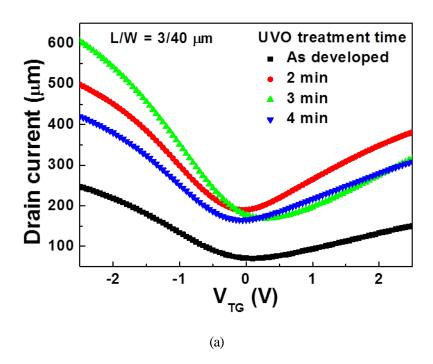

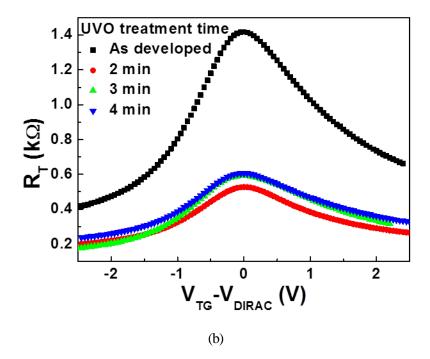

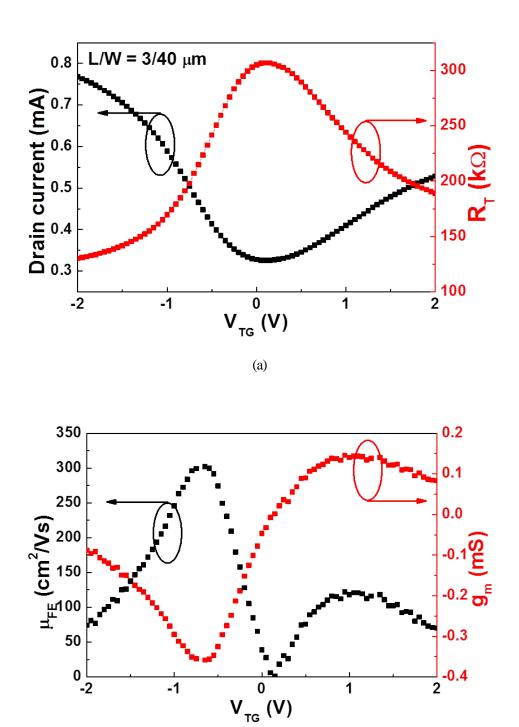

- Figure 4.5. (a) Drain current as a function of  $V_{TG}$ - $V_{Dirac}$  ( $I_D$ - $V_G$ ) (b) total resistance as a function of  $V_{TG}$ - $V_{Dirac}$  ( $R_T$ - $V_G$ ); for BG-GFETs with UVO<sub>3</sub> treated contact.

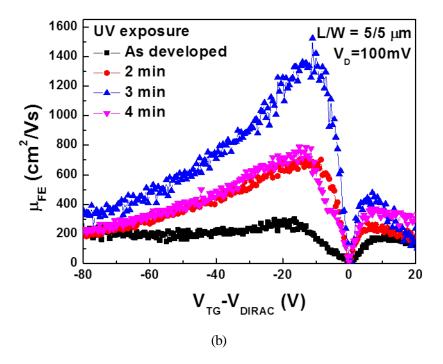

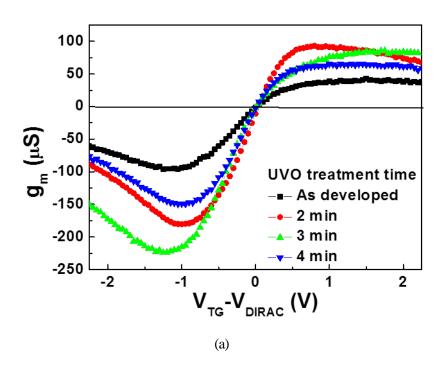

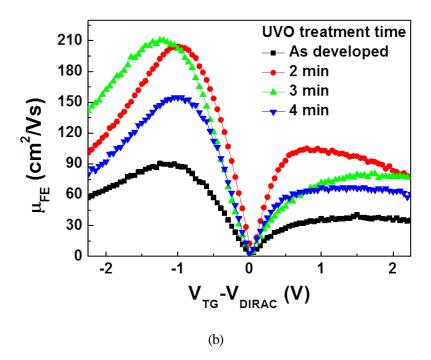

- Figure 4.6. (a) Transconductance and (b) field effect mobility; as a function of  $V_{TG}$ - $V_{Dirac}$  for BG-GFETs with UVO<sub>3</sub> treated contact.

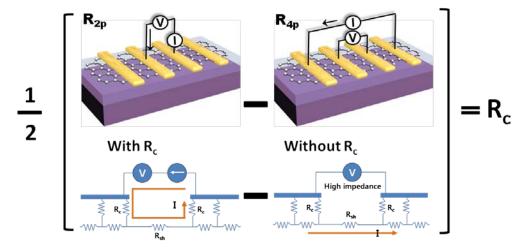

- Figure 4.7. Schematic diagram how to extract the contact resistance.

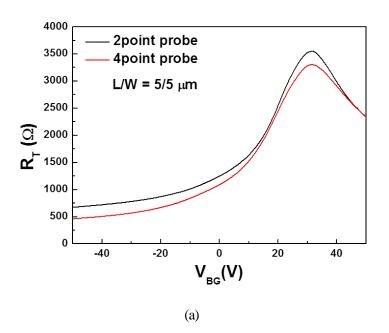

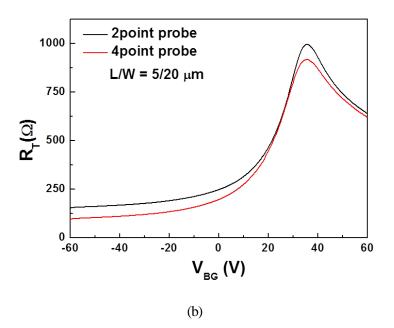

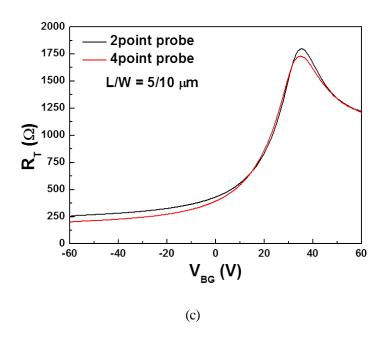

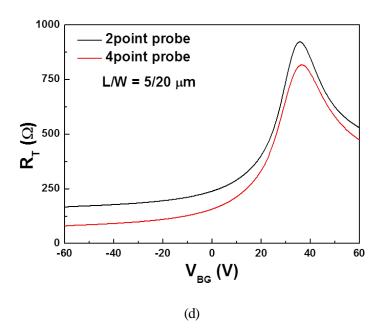

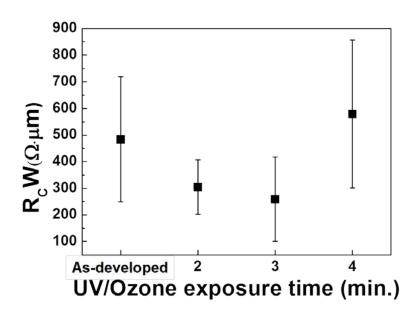

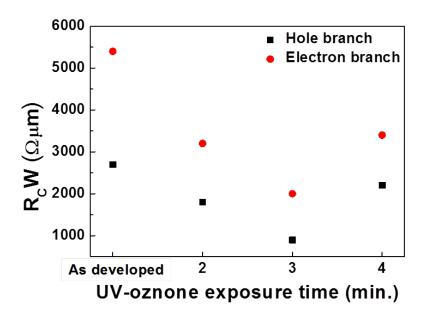

- Figure 4.8. Total resistance as a function of back gate voltage using two and four point probe method for BG-GFETs with (a) as-developed (b) UVO<sub>3</sub> for 2 min (c) UVO<sub>3</sub> for 3 min (d) UVO<sub>3</sub> for 4 min.

- Figure 4.9. Normalized contact resistance as a function of UVO<sub>3</sub> treatment time in BG-GFETs.

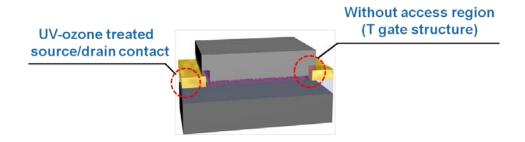

- Figure 5.1. GFETs with ungated region.

- Figure 5.2. Schematic diagram of proposed TG-GFETs.

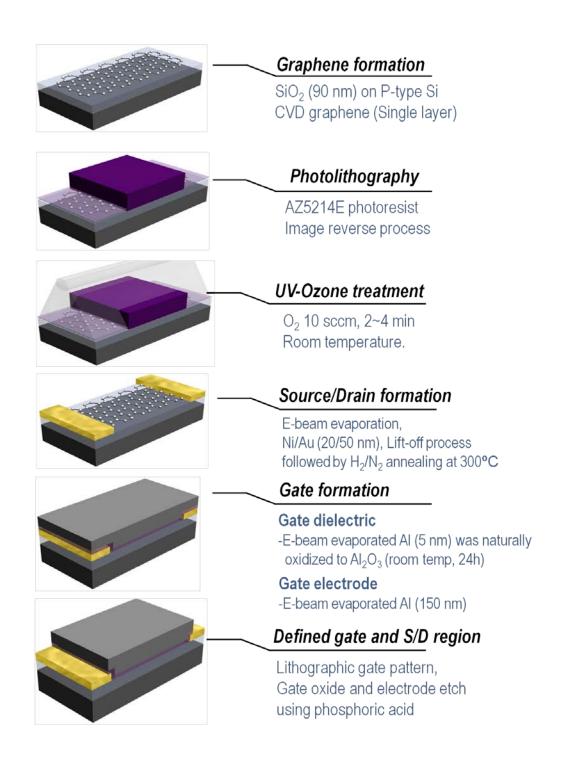

- Figure 5.3. Fabrication sequence of TG-GFETs with overlapped S/D to gate and UVO<sub>3</sub> treated contacts.

- Figure 5.4. (a) Transfer characteristics of the drain current as a function of the top gate voltage ( $I_D$ - $V_{TG}$ ) and (b) total resistance as a function of the gate voltage ( $R_T$ - $V_G$ ) of GFETs with overlapped S/D to gate structure and UVO<sub>3</sub> treated contacts.

- Figure 5.5. (a) Transconductance and (b) filed effect mobility of GFETs with overlapped S/D to gate structure and UVO3 treated contacts.

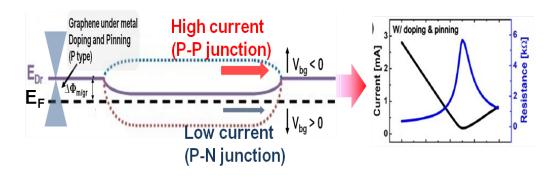

- Figure 5.6. Schematic of band diagram in graphene under metal with doping and pinning.

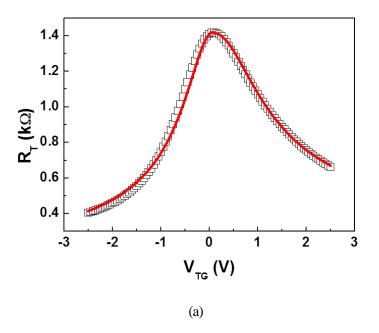

- Figure 5.7. Measured  $R_T$  versus  $V_G$  (black square) of GFETs with overlapped S/D to gate structure and UVO<sub>3</sub> treated contacts (a) as developed (b) for 2 min (c) for 3 min (d) for 4 min and fitted result (red line) with equation, respectively.

- Figure 5.8. Normalized contact resistance as a function of UVO<sub>3</sub> exposure time in TG-GFETs.

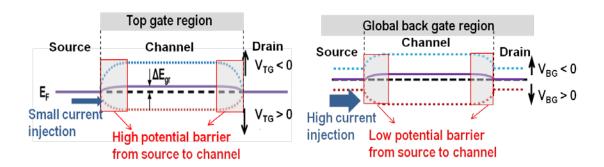

- Figure 5.9. Schematics of band diagram of TG-GFET versus BG-GFET.

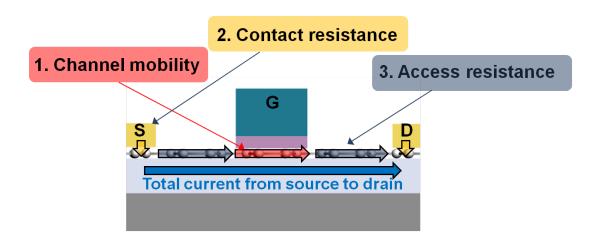

- Figure 6.1. Schematic of three primary parameters in GFET.

- Figure 6.2. Fabrication sequence of TG-GFETs with solution-processed gate dielectric,  $UVO_3$  treated contact and overlapped S/D to gate structure.

- Figure 6.3. (a) Drain current and total resistance ( $R_T$ ) and (b) Transconductance and field effect mobility as a function of gate voltage.

- Figure 6.4. Total resistance  $R_{\rm T}$  versus gate voltage  $V_{\rm G}$  (black square) of the proposed GFETs and fitted result (red line) with equation (3.2), respectively.

# **List of Table**

- Table 3.1. Comparison of the intrinsic carrier mobilities and residual carrier concentration at various PDA temperatures.

- Table 6.1. Comparison of transconductance and field effect mobility of fabricated device in the work.

- Table 6.2. Comparison of intrinsic mobility and contact resistance of fabricated device in the work.

1

## Introduction

#### 1.1 Limitation of MOSFET Scaling

Since their beginning of early 1970's, silicon-based transistors have been successfully developed by downsizing the MOSFETs (Metal Oxide Semiconductor Field Effect transistors) according to the Moore's law [1,2]. In this law, the number of transistors in integrated circuits is doubled with every two years. As the MOSFET feature size scales down, the number of integrated circuits within a same size wafer exponentially increased, resulting in significant decrease of the production cost per transistor. The scaling down is still a most effective and important strategy for realizing high performance and low power consumption in MOSFETs up to now. Consequently, the technology node in mass production reached 14 nm in 2014.

While the scaling strategy has undoubtedly led to remarkable developments in semiconductor industry, it is also true that conventional MOSFET technology is facing physical and technological limits of scaling as the gate length ( $L_G$ ) of the transistors becomes the order of few nanometer in size [3-7]. The challenges being faced are:

- a) Subthreshold swing (SS) degradation

- b) Threshold voltage ( $V_{Th}$ ) roll-off

- c) Drain-induced barrier lowering (DIBL)

- d) Band-to-band tunneling (BTBT)

The thickness of the gate dielectrics has also been reduced concurrently to gain high enough current at low operation voltages. For thicknesses below 20 Å, however, the quantum mechanical direct tunneling occurs, resulting in significant increase of the gate leakage current into the gate oxide [8,9]. Consequently, the standby power consumption in devices in such ultrathin gate dielectrics increases exponentially, causing a most serious problem.

To solve these problems, a variety of new technology and materials are being developed, which include use of 3D structure, R-CAT (Recessed-Channel Array Transistor), high-k gate dielectrics, metal gate, ultra-shallow source/drain junctions, and strained silicon. Despite these efforts, however, many researchers are finding unbeatable physical limits for gate length less than 5 nm. We are therefore forced to find new solutions by employing alternative channel materials such as III-V compound semiconductor, carbon nanotube (CNT) and graphene. Among these materials, graphene is a strongest candidate to replace the silicon-based devices as a channel material due to its outstanding electrical properties.

#### 1.2 Graphene as an Alternative Material

#### 1.2.1 Structural Properties of Graphene

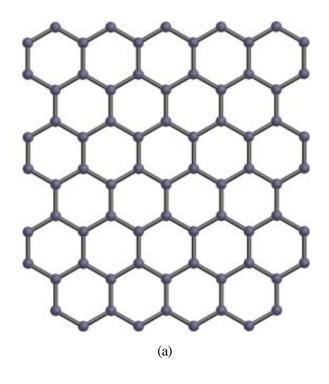

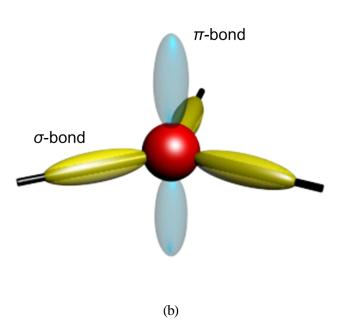

Graphene is a flat monolayer of  $sp^2$ -bonded carbon atoms with a hexagonal honeycomb lattice. Graphene is a basic structural element of carbon allotropes such as graphite, carbon nanotubes and fullerenes. One carbon atom contains six electrons with a configuration of  $1s^2 2s^2 2p^2$ . Among these, the outer four  $2s^2 2p^2$  electrons act as the valence electrons. In graphene, one 2s orbital interacts with the  $2p_x$  and the  $2p_y$  orbitals to form three  $sp^2$ -hybridized orbitals. These three orbitals are used to form three  $\sigma$ -bonds with the neighboring carbon atoms. They are directly linked within the a-b plane with angles of 120 degrees each other, resulting in the hexagonal structure of graphene [in Fig. 1.1 (a)]. This honeycomb structure gives a record breaking strength and excellent mechanical properties to graphene because the  $\sigma$ -bond is the strongest among the covalent bonds. The remaining valence electron sits in the  $p_z$  orbital, which is perpendicular to the graphene plane.  $\pi$ -electrons in graphene are relatively delocalized and weakly bound to the nuclei. The exceptional electronic properties in graphene are caused by this delocalized nature of  $\pi$  electrons [10].

Figure 1.1. (a) Atomic structure of graphene. (b)  $\pi$ - (blue) and  $\sigma$ - bonds (yellow) in graphene.

#### 1.2.2 Electrical Properties of Graphene

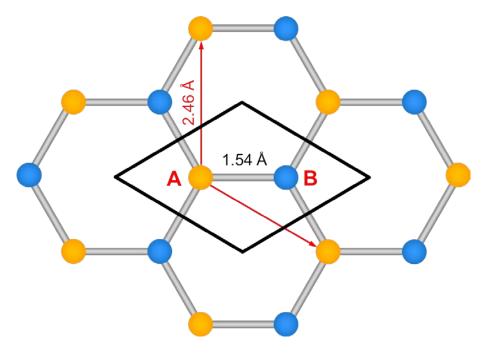

Graphene is a 2D honeycomb lattice made of carbon atoms. This honeycomb lattice can be characterized with a basis of two atoms, labeled A and B in Figure 1.2. The primitive unit cell is an equilateral parallelogram with the lattice constant of a = 2.46 Å. Because the unit cell consists of two carbon atoms, the energy spectrum originating from the  $\pi$  orbitals has two bands and these  $\pi$  electrons per unit cell contribute to the electrical properties of graphene. The band structure of graphene can be described using a nearest neighbor tight-binding model as follows [11,12]:

$$E(k_x, k_y) = \pm \gamma \sqrt{1 + 4\cos(\frac{\sqrt{3}ak_x}{2})\cos(\frac{ak_y}{2}) + 4\cos^2(\frac{ak_y}{2})},$$

(1.1)

where a is the lattice constant and  $\gamma$  is the nearest neighbor hopping energy.

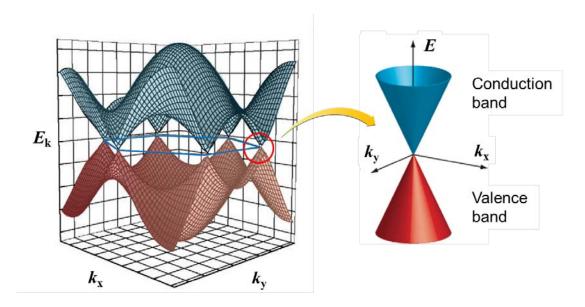

Figure 1.3 shows the band structure of graphene by 3D plot of the nearest neighbor tight-binding dispersion. The upper half is the conduction ( $\pi^*$ ) band and the lower half is the valence ( $\pi$ ) band. The valence band is completely filled by electrons and the conduction band is empty. In Fig. 1.3, it is confirmed that the top of the valence band and the bottom of the conduction band meet at a point K, called the Dirac point. Graphene, therefore, is considered as a semi-metal or zero-bandgap material due to absence of the bandgap at the Fermi energy [13].

Around these K-points, the dispersion can be expressed as a linear relation as

$$E(|k|) = \pm \hbar v_F |k|, \tag{1.2}$$

where  $\hbar$  is the reduced Plank constant and  $\nu_F$  is the Fermi velocity. The value of  $\nu_F$  is about c/300, with c being the speed of light. This dispersion relation implies that the carriers behave like a massless Dirac particle with a very large Fermi velocity [14]. These properties are in sharp contrast with those of classical semiconductors having a dispersion of  $E = p^2/2m^*$ , where  $m^*$  is the effective mass of the electrons.

The density of states (DOS) is an important property of electronic materials, which gives the

density of mobile electrons and holes present in the solid at a given temperature. In graphene, the DOS g(E) is given by the following equation [13,15]:

$$g(E) = \frac{2}{\pi (\hbar v_F)^2} |E|, \qquad (1.3)$$

where the energy E is measured from the Fermi energy  $E_{\rm F}$ . From this equation, it is noted that the DOS value is zero at the Fermi energy ( $E_{\rm F}=0$ ). This is the difference between graphene and regular metals that have large DOS at the Fermi energy.

The sheet carrier density in graphene can be expressed using g(E) as

$$n = \int_0^\infty g(E) f(E_F) dE, \qquad (1.4)$$

where  $f(E_F)$  is the Fermi-Dirac distribution given by  $f(E_F) = \{1 + \exp[(E - E_F) / k_B T]\}^{-1}$ ,  $k_B$  the Boltzmann constant and T the absolute temperature. Then, the sheet carrier density  $n_i$  in graphene is given by:

$$n_i = \frac{\pi}{6} \left(\frac{k_B T}{\hbar v_F}\right)^2 \approx 9 \times 10^5 T^2 \text{ (electrons/cm}^2).$$

(1.5)

From this equation, the sheet carrier density in graphene is shown to have a squared-power dependence to T, in contrast to semiconductors having an exponential dependence on T. The only material-specific parameter is the Fermi velocity  $v_{\rm F}$ . The intrinsic sheet carrier density of  $n_{\rm i} \approx 8 \times 10^{10}$  cm<sup>-2</sup> is obtained at room temperature.

Figure 1.2. Lattice structure of graphene with basis of two atoms denoted as A and B.

Figure 1.3. Band structure of graphene.

#### 1.3 Graphene FET applications

As mentioned above, graphene has been attracting considerable interest for various applications such as transparent electrodes, sensors, solar cells, and transistors due to its outstanding electrical, optical and mechanical properties. Especially, a number of researchers have focused on development of graphene field-effect transistors (GFET) to replace conventional silicon-based devices because it is considered to show the highest charge carrier mobility of existing materials.

The first GFET device was reported by a Manchester group in 2004 [16]. They fabricated a back-gate type GFET by transferring an exfoliated graphene layer onto a Si substrate covered with a 300-nm SiO<sub>2</sub>, and confirmed the occurrence of the field-effect modulation of carriers. Although these back-gated transistors have been very effective for the proof-of-concept purposes, they are not suitable for practical integrated circuits (IC) [17]. Practical GFETs need a top-gate structure. The first top-gated GFET was reported by Lemme *et al.* in 2007 using exfoliated graphene [18]. Since then, there have been numerous reports on top-gated GFETs using exfoliated graphene [19], graphene grown on metal substrates [20], and epitaxial graphene [21] to name a few. Even a wafer-scale graphene circuit was demonstrated in 2011 [22]. All these results strongly suggest possible use of graphene in the future electronic devices. Since its discovery in 2004, graphene has thus achieved splendid and skyrocketing developments in IC technology, which can be compared to other materials such as CNT, III-V compound semiconductor [17].

#### 1.3.1 GFETs for logic applications

Graphene is a promising alternative to Si-based transistors owing to its exceptional electrical characteristics. They include ultrahigh carrier mobility and ability to form ultrathin channels, which permit both scaling down to even shorter channel lengths without detrimental short-channel effects as well as ability to realize high enough performance without further risky scaling down. There are however several issues in order for graphene to be applied in logic devices. The most important issue should be the fact that graphene is a semimetal with no band gap. In graphene, the valence and the conduction bands meet at a single point called Dirac point (Fig 1.3), which leads to miserably small on/off current ratios. To solve the problem, a number of researchers have been focused on development of bandgap engineering in graphene for applications of logic devices.

Among the most used techniques, graphene nanoribbon (GNR) with narrow width is one of the most promising approaches to open the bandgap (Fig 1.4) [23]. If width of GNR is below 10 nm, a bandgap of ~eV will be opened in graphene, which is enough to fabricate GFETs with on/off ratios of 10<sup>7</sup> or more at room temperatures [24]. To accomplish large scale production of GNR, numerous studies have been conducted such as electron beam lithographic patterning [25], cutting oxidized graphene [26], chemical synthesis [23], and scanning tunneling microscopy lithography [27].

A variation of this GNR strategy is to use a graphene nanomesh (GNM) structure, in which an array of nanoholes are interconnected with GNR networks on the graphene sheet surface (Fig 1.5). This GNM-based FETs not only support the driving currents that are ~100 times greater than that of individual GNR based FETs but can be fabricated with much easier process as compared to GNR [28, 29].

Graphene bilayer FETs [30] have also been suggested to open the band gap in graphene. Although it has been extensively investigated experimentally and by device simulations, the on/off ratio of bilayer GFETs is not yet large enough for applications in logic devices.

Figure 1.4. (a) Schematic of cutting the graphene sheet to obtain zigzag and armchair GNR (b) Transfer characteristics for a width of 5 nm and channel length of 130 nm GNR with Pd contacts and Si backgate. [24]

Figure 1.5. (a) Schematic of GNM-FET (b) Transfer characteristics for GNMs with different estimated neck width of 15, 10 and 7 nm. [29]

#### 1.3.2 GFETs for RF applications

As stated above, absence of the bandgap in GFET makes it difficult to switch off the current and is not best suitable for logic devices. In this context, graphene has found much more substantial interests in radio-frequency (RF) applications, in which a high on/off ratio is not essentially required. Significant progress has been therefore made on GFETs in RF applications. In realizing high performance in RF-FETs, it is not only the channel material with excellent carrier transport properties that matters, but minimizing the extrinsic parameters such as parasitic capacitance, the access resistance, and the contact resistance at the source/drain electrodes. Further scale down of the channel length is of course important. Since the first graphene RF transistors with a cut off frequency ( $f_T$ ) of gigahertz was reported in 2008 [31], intensive efforts have been made on improvement of graphene-based RF transistors by changing the device structure to minimize the series resistances (contact and access) and the parasitic capacitance, and the gate length. Now the highest  $f_T$  reported for graphene RF transistors is 427 GHz [32]. However, this value is not as high as those of competing semiconductors such as InP high electron mobility transistor (HEMT) and GaAs metamorphic HEMT (mHEMT) (Fig.1.6) [17]. Therefore, we should develop further technologies for application of high performance graphene RF transistors.

Figure 1.6. Comparison of cut off frequency between GFET and other devices, as a function of gate length  $L_{\rm G}$  [17].

#### **1.4 Challenges on GFETs**

As stated above, graphene has been attracting explosive attention as a candidate for the new channel material owing to its extraordinary electrical properties, such as ultra-high carrier mobility and the 2D structure. As we have seen in section 1.3, GFET technologies have developed rapidly, which include the bandgap engineering, scaling of the gate length, novel device structures for high speed and frequency FET, in the past few years. As a result, GFETs are considered as a promising alternative for post-silicon electronics.

To develop high performance GFETs, however, many challenges still remain to be overcome for practical industrial applications. MOSFETs are basically three terminals devices, consisting of gate, source and drain. In Si technology, the gate electrode, metal or doped Si, is separated from the channel material via an insulating layer such as silicon dioxide or high-k materials. The charge carriers, electrons or holes, in the channel region are induced by an electric filed. When the drain voltage is applied, the carriers in the source (drain) region will flow through the channel to the drain (source) terminal. This is the performance of FET, i.e., control of the channel conductivity by the gate electric field and of the current between source and drain. With an extremely high mobility, graphene certainly has a great potential for high speed FETs. However, the excellent intrinsic properties of graphene are significantly deteriorated in actual GFETS, due to adverse effects caused during the fabrication process such as deposition of gate insulator and metals on graphene as well as annealing and lithographic processes. The GFET research is thus being focused on achieving high cut off frequency and high field effect mobility without losing the excellent properties of pristine graphene.

In FETs,  $f_T$  and  $\mu_{FE}$  are expressed by the following equations, respectively.

$$f_T = \frac{1}{2\pi} \frac{g_m}{C_G},\tag{1.6}$$

$$\mu_{FE} = g_m \frac{L}{W} \frac{1}{C_{OX} V_d}.$$

(1.7)

As can be seen in equations 1.6 and 1.7, the transconductance  $(g_m)$ , defined by the ratio of the drain current variation to that of the gate voltage, is proportional to both  $f_T$  and  $\mu_{FE}$ . Thus, we notice that high  $f_T$  and  $\mu_{FE}$  values are obtained by a high transconductance. For obtaining a high transconductance, it is in turn required to decrease the impurities in the channel region [33] and the access and the contact resistances [34,35].

Aiming at betterment of the performance in GFETs, I have focused on the following topics in this study:

- a) Development of a novel gate dielectric deposition method, i.e., a solution process, for minimizing the doping, strain, defects in graphene during the gate dielectrics deposition.

- b) Systematic investigation on the removal of contamination on graphene by use of oxygen plasma for low contact resistance.

- c) Development of the overlapped S/D technology to reduce the access resistance.

#### 1.5 Outline

The outline of this thesis is as follows. Chapter 2 describes development of a solution method for Al<sub>2</sub>O<sub>3</sub> dielectric layers. Raman evaluation of the doping, strain, and defects in graphene caused by the formation of the solution-processed Al<sub>2</sub>O<sub>3</sub> as well as its electrical characteristics such as dielectric constant, breakdown voltage and leakage current will also be presented. It will be shown that a modified solution process, consisting of insertion of an ultrathin Al<sub>2</sub>O<sub>3</sub> seeding layer, spin-coating, oxygen plasma treatment, post-deposition annealing (PDA) at 250 °C for 2 hours, gives the minimum doping, strain and defects to graphene and its excellent electrical characteristics.

Chapter 3 describes the fabrication of top-gated GFETs using the modified solution process method. Evaluations will be made for various PDA temperatures. We obtain a high intrinsic carrier mobility of 8400 cm<sup>2</sup>/Vs when the PDA temperature is set at 250 °C, at which the defect density, hole doping, and stain in the graphene channel layer are minimized. The field-effect mobilities, however, are low in all devices. This can be attributed to a high series resistance consisting of the contact resistance between graphene and the metal electrodes and the access resistance under the ungated region between the gate and the source/drain electrodes.

Chapter 4 describes the effects of ultraviolet-ozone (UVO<sub>3</sub>) treatment for reducing the contact resistance through removal of the interfacial contaminations. To remove the photoresist (PR) residue without introducing substantial damages to graphene, we carried out several analyses on graphene as a function of the UVO<sub>3</sub> time: the surface morphology by atomic force microscopy (AFM) and defects by Raman scattering spectroscopy. The contact resistance was evaluated independently by use of 2-and 4-point probe methods on back-gate GFETs. As a result, 3 min operation of the UVO<sub>3</sub> treatment was found to be the best; the surface morphology is identical with pristine graphene and the defect density was only slightly increased. The contact resistance on this graphene ranges from 100 to 400 Ωμm, which is comparable to one of the best reported values.

In chapter 5, the UVO<sub>3</sub> treated contacts will be applied to fabricate the overlapped S/D to topgate devices for reducing the series resistance including the access and the contact resistance. After 3 min of the UVO<sub>3</sub> treatment, we obtain a lowest contact resistance of 900  $\Omega\mu$ m, comparable to one of the best reported values, as well as substantial betterment in the field-effect mobility.

Finally, chapter 6 describes the fabrication and characterization of top-gated GFETs, consisting of modified solution-processed gate dielectrics, UVO<sub>3</sub>-treated contacts, and overlapped S/D to gate structure. As a result, highest transconductance of 358 μS and a field-effect mobility of 301 cm<sup>2</sup>/Vs, not achievable by either the solution-gate or the UVO<sub>3</sub> treated contacts alone, have been obtained. These high transcondcutance and the field-effect mobility values are attributed to both increase of intrinsic mobility and reduction of the contact resistance. The intrinsic mobilities are actually as high as 8620 cm<sup>2</sup>/Vs for holes and 8650 cm<sup>2</sup>/Vs for electrons.

#### Reference

- [1] G. E. Moore, Electronics **38**, 114 (1965).

- [2] E. J. Nowak, IBM Journal of Research and Development 46, 169 (2002).

- [3] B. Davari, R. H. Dennard and G. G. Shahide, Proc. IEEE 89, 595 (1995).

- [4] S. Asai and Y. Wada, Proc. IEEE 85, 505 (1997).

- [5] Y. Taur, D. Buchanan, W. Chen, D. Frank, K. Ismail, S.-H. Lo, G. Sai-Halasz, R. Viswanathan, H.-J. C. Wann, S. Wind and S.-H. Wong, Proc. IEEE 85, 486 (1997).

- [6] P. K. Bondy, Proc. IEEE 86, 78 (1998).

- [7] D. Frank, R. Dennard, E. Nowak, P. Solomon, Y. Taur and H.-S. Wong, Proc. IEEE 89, 258 (2001).

- [8] Y. T. Lou, M. F. Li, Y. Jin and W. H. Lai, Journal of Applied Physics 91, 258 (2002).

- [9] C.-Y. Chang, C.-C. Chen, H.-C. Lin, M.-S. Liang, C.-H. Chien and T.-Y. Huang, Microelectronics Reliability 39, 533 (1999).

- [10] J.-C. Charlier, X. Blase, and S. Roche, Review of Modern Physics 79, 677 (2007).

- [11] P. R. Wallace: Physical Review **71**, 662 (1947).

- [12] S. Reich, J. Maultzsch and C. Thomsen, Physical Riview B 66, 035412 (2002).

- [13] A. H. Castro Neto, F. Guinea, N. M. R. Peres, K. S. Novoselov and A. K. Geim, Review of Modern Physics 81, 109 (2009).

- [14] T. Ando, Journal of Physics Society of Japan 74, 777 (2005).

- [15] E. H. Hwang and S. Das Sarma, Physical Review B. **79**, 165404 (2009).

- [16] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva and A. A. Firsov, Science 306, 666 (2004).

- [17] F. Schwierz, Proceedings of the IEEE **101**, 1567 (2013).

- [18] M. C. Lemme, T. J. Echtermeyer, M. Baus and H. Kurz, IEEE Electron Device Letters 28, 282

(2007).

- [19] L. Liao, Y.-C. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K. L. Wang, Y. Huang and X. Duan, Nature 467, 305 (2010).

- [20] Y. Wu, Y.-M. Lin, A. A. Bol, K. A. Jenkins, F. Xia, D. B. Farmer, Y. Zhu and P. Avouris, Nature 472, 74 (2011).

- [21] Y.-M. Lin, C. Dimitraopoulos, K. A. Jenkins, D. B. Farmer, H.-Y, Chiu, A. Grill and Ph. Avouris, Science 327, 662 (2010).

- [22] Y.-M Lin, A. Valdes-Garcia, S.-J. Han, D. B. Farmer, I. Meric, Y. Sun, Y. Wu, C. Dimitrakopoulos, A. Grill, P. Avouris and K. A. Jenkins, Science 332, 1294 (2011).

- [23] Y.-W. Son, M. L. Cohen and S. G. Louie, Physical Review Letters 97, 216803 (2006).

- [24] X. Li, X. Wang, L. Zhang, S. Lee and H. Dai, Science **319**, 1229 (2008).

- [25] Z. Chen, Y.-M, Lin, M. J. Rooks and P. Avouris, Physica E 40, 228 (2007).

- [26] S. Fujii and T. Enoki, Journal of the American Chemical Society 132, 10034 (2010).

- [27] G. Z. Magda, X. Jin, I. Hagymasi, P. Vancso, Z. Osvath, P. Nemes-Incze, C. Hwang, L. P. Biro and L. Tapaszto, Nature 514, 608 (2014).

- [28] J. Bai, X. Duan and Y. Huang, Nano Letters 9, 2083 (2009).

- [29] J. Bai, X. Zhong, S. Jiang, Y. Huang and X. Duan, Nature nanotechnology 5, 190 (2010).

- [30] F. Xia, D. B. Farmer, Y.-M. Lin and P. Avouris, Nano Letters **10**, 715 (2010).

- [31] I. Meric, N. Baklitskaya, P. Kim and K. L. Shepard, IEEE International Electron Devices Meeting 2008. p. 1-4

- [32] R. Cheng, J. Bai, L. Liao, H. Zhou, Y. Chen, L. Liu, Y.-C. Lin, S. Jiang, Y. Huang and X. Duan, Proceedings of the National Academy of Sciences **109**, 11588 (2012).

- [33] M. Miyamoto, K. Toyota, K. Seki and T. Nagano, IEEE Transactions on Electron Devices 46, 1699 (1999).

[34] L. H. Hess, M. V. Hauf, M. Selfert, F. Speck, T. Seyller, M. Stutzmann, I. D. Sharp and J. A. Garrido, Applied Physics Letters **99**, 033503 (2011).

[35] K. N. Parrish and D. Akinwande, Applied Physics Letters 98, 183505 (2011).

# Solution-processed gate dielectrics for GFETs

#### 2.1 Introduction

One of the main reasons for the success of Si integrated circuits sits in the ideal interface between Si and its thermally grown oxide. The low interface trap density, the large bandgap offsets with Si, and the high breakdown reliability of the thermally grown silicon dioxide have made Si a platform for integrated circuits. These merits of Si more than compensate its mediocre carrier mobilities as compared to those of competing semiconductors such as Ge and GaAs [1,2]. The same situation applies to graphene, an emerging channel material for the next generation electronic devices. Despite its excellent carrier mobility [3,4] that leads to a wide variety of potential applications [5-7], the absence of graphene's natural oxide available as a gate insulator in GFETs leaves a critical issue toward industrialization of graphene in electronics. Deposition of dielectrics onto graphene, on the other hand, suffers difficulties from chemically inert (hydrophobic) nature of graphene [8,9], induced damages during plasma processings [10], and onsets of strain and doping during high temperature post-deposition annealings (PDA) [11,12]. Choice of right dielectric materials and of damage-free deposition techniques is key to realization of GFETs.

Doping during high-temperature annealing has been recently reported by Ryu et al.[13], who clarified that a substantial hole doping occurs in graphene under oxygen ambient at temperatures above 290 °C. They pointed out a correlation of this p-type doping to formation of bondings between oxygen and graphene's carbon atoms, which causes charge transfer from graphene to oxygen atoms.

If this is the case, lowering of the deposition and the PDA temperatures could substantially suppress the hole doping and enhance the mobility as well. In this context, we have noticed that a solution-process for gate dielectrics, consisting of a spin-coating of precursor liquid followed by PDA, should be advantageous. Solution-processed, or sol-gel, high-k gate dielectrics have been widely used in fabrication of organic thin-film transistors (OTFTs). No studies, however, have ever been made on this solution process to fabricate GFETs.

In this chapter, we examine the applicability of the sol-gel method for the gate dielectrics process in GFETs. We propose a "modified sol-gel method" (Fig 2.1), consisting of initial formation of natural oxide of Al, spin-coating of sol-gel precursor for  $Al_2O_3$ , oxygen-plasma treatment, and PDA at 250 °C, as a process best suited for formation of GFET dielectrics.

Figure 2.1. Composition of modified solution-processed gate dielectrics

#### 2.2 Raman Evaluation of Doping and Strain in Graphene

#### 2.2.1 Principle of Raman scattering spectroscopy

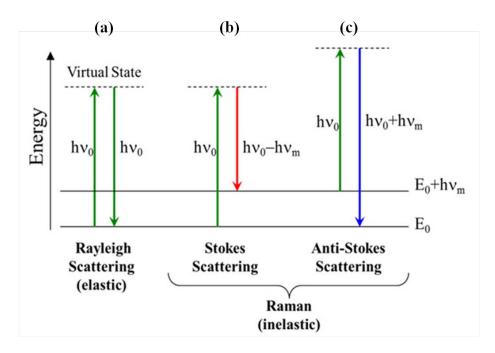

When incident light is applied to molecules, molecules will be excited into their higher energy states. The molecules in excited states drop to ground states through three mechanisms. Small particles with very small size compared to the wave length of incident radiation scatter the incident light almost equally into its backward direction. This type of scattering is called Rayleigh scattering (Fig 2.2(a)). Another type of scattering in which the scattered photon has either lower or higher energy than that of the incident light is called Raman scattering. Raman scattering effect was first reported by C. V. Raman and K. S. Krishnan. In Raman scattering, the difference in energy between incident and scattered photons corresponds to the energy required to excite a molecule to a higher vibrational mode.

If electromagnetic radiation is applied to molecules, energy is transferred according to the Bohr's quantum condition. We can express this using the following equation.

$$\Delta E = h\nu = h\frac{c}{\lambda},\tag{1-1}$$

where  $\Delta E$  is the difference in energy between the two quantized states, h is the Plank's constant, c is the speed of light and  $\lambda$  is wavelength. This energy difference is identical with the energy difference between the two quantized states:

$$\Delta E = E_2 - E_1 \quad , \tag{1-2}$$

where  $E_2$  is energy of excited state and  $E_1$  is energy of ground state. Therefore, molecules are excited by absorption of the energy  $\Delta E$  or de-excited by emission of energy  $\Delta E$ . For the former case, the molecules absorb energy, and the scattered light loses just this amount of energy. The emitted photon has a lower energy than it had before. This type is called Stokes scattering (Fig 2.2(b)). On the other hand, if the already excited molecules lose part of their energy during their interaction with photons, the emitted photon has a higher energy than it had before. This type is called anti-Stokes scattering (Fig 2.2(c)). The latter process is much more rare at room temperature, because most molecules are in their ground state. Thereby, Stokes scattering peaks are stronger than anti-Stokes scattering.

In spectroscopy, it is a common practice to use wave number ( $\overline{\nu}$ , cm $^{-1}$ ) instead of wavelength, or frequency, or energy of the light. The wave number and speed of light are described the following relation

$$\overline{v} = \frac{v}{c} = \frac{1}{\lambda},\tag{1-3}$$

From equations 1-1, 1-2 and 1-3, variation of measured energy is expressed the following formula.

$$\Delta E = E_2 - E_1 = hc\overline{v} \ . \tag{1-4}$$

Figure 2.2. Quantum energy transitions for Rayleigh and Raman scattering.

#### 2.2.2 Raman spectrum of graphene

By using Raman spectroscopy, we can obtain the phonon energy and the corresponding symmetry of the vibrational mode, resulting in obtaining the information of lattice structure of the material. In particular, Raman signal from graphene is very strong because graphene layer has a conical dispersion with a zero-band gap [14]. For this reason, we can easily detect the Raman signal of a graphene layer even though graphene has a single atom thickness.

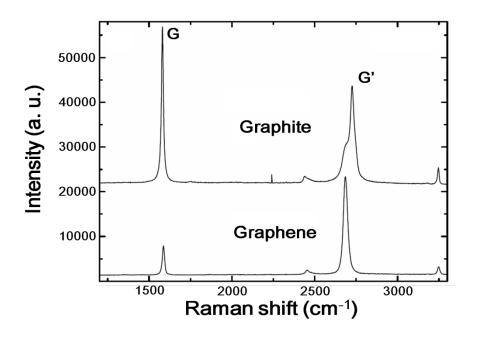

Figure 2.2 shows a typical Raman spectra obtained for graphite and graphene. Two most intense features can be observed: the central peak is 1580 cm<sup>-1</sup> and 2700 cm<sup>-1</sup>, named G and G' (or 2D) band, respectively. In case of a disordered graphene or at the edge of graphene's grain, we also observe a D-band peak at around 1350 cm<sup>-1</sup>, not shown in Figure 2.3.

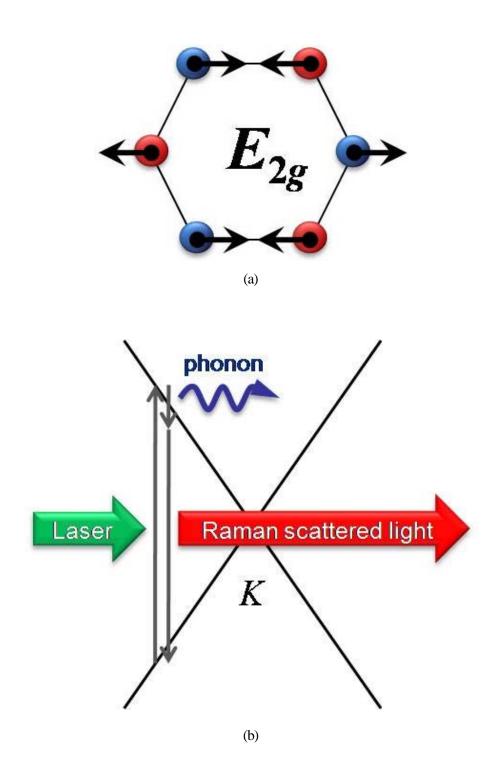

The G band of graphene corresponds to a doubly degenerate phonon mode,  $E_{2g}$  symmetry, at the Brillouin zone (Fig 2.4(a)). The G band is only originating from a conventional first order Raman scattering process in graphene [15]. Figure 2.4 (b) shows the first-order G-band process in graphene. The incident radiation excites electrons from valence band to the conduction band. The excited electron is scattered by phonons of wave vector q and then electron and hole recombine, emitting scattered photon. Thus, the energy of difference between incident light and emitted photon corresponds to energy of phonon. In order to conserve the momentum, the mode at the Brillouin zone center, which located center of  $\Gamma$  point contributes to the Raman scattering because the light momentum is very small compared to the reciprocal Brillouin zone.

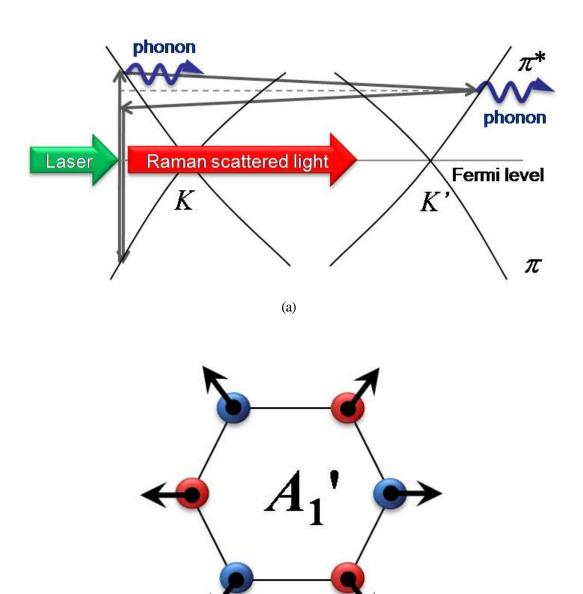

The G' band of graphene come from a second-order double resonant process [15]. As have seen Figure 2.5(a), the incident light excites electrons from valence band to conduction band. The electron is scattered by phonon of wave vector q from K to K' point. Since the Raman process must conserve energy and momentum, the electron must scatter back to K state before recombining with the hole. The electron thus is scattered back to the k state, and emits a photon by recombining with a hole at a k

state. This scattering process is second-order Raman scattering, involving two real electronic states of K and K' point and the G' peak of graphene is strongly generated in Raman spectrum.

The D band is due to  $A_1$ ' vibration mode as shown in Figure 2.5 [16]. This mode can't be observed in complete lattice structure because of symmetry. The D band involves an phonon around the K-point like G' band. However, the D band requires a defect for the momentum conservation. Therefore, D band is rarely observed in exfoliated graphene with lower defect. On the other hand, in case of CVD (Chemical vapor deposition) graphene, D band can be generally examined in Raman spectrum.

Figure 2.3. Raman spectrum of graphite and monolayer graphene [14].

Figure 2.4. (a) G band vibration modes for the iTO (in-plane transverse optical) phonons at the  $\Gamma$ -point (b) First-order Raman scattering process.

Figure 2.5. (a) Second-order Raman scattering process. (b) D band  $A_1$ ' vibration mode for the iTO phonon at the K-point.

(b)

#### 2.2.3 Raman spectrum in doped graphene

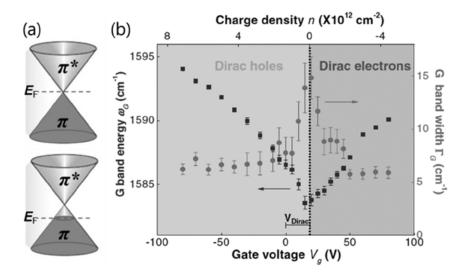

Theoretically, the Fermi level is identical to the Dirac point in ideal, undoped graphene at 0 K. When extra electrons are induced in graphene, however, they will show strong effects on electrical properties because of the unique electronic structure of graphene. Figure 2.6 (a) shows the electronic band structures of undoped (upper) and p-type doped (lower) graphene. The Fermi level is significantly lowered in the latter even to accommodate small amount of holes because the density of state is very small in the vicinity of the vertex of the  $\pi$ -  $\pi$ \* electronic bands in this conical shape [17]. Figure 2.6 (b) shows the Raman G peak position as well as its peak width as a function of the gate voltage  $V_{\rm g}$  measured at 295K [18]. The G peak position is shifted to higher energies with increase of the carrier (electron or hole) concentration. As one can observe, the peak position of the Raman G peak is quite sensitive to the carrier concentration.

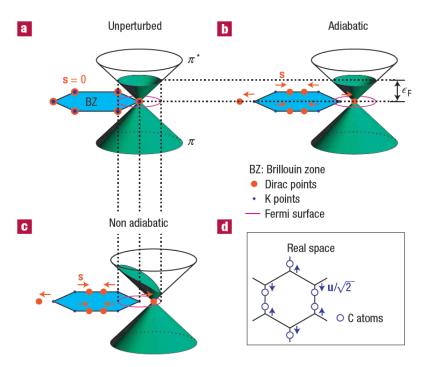

Adiabatic Born-Oppenheimer approximation (ABO) can be valid when electrons are much lighter than nuclei (Fig 2.7(b)) [19]. In the dynamical sense, electrons can be regarded as particles that follow the nuclei motion  $(u/\sqrt{2})$  adiabatically (Fig 2.7(d)), that is, they are dragged along with the nuclei without requirement of a finite relaxation time. However, ABO is no longer valid when the atomic motion is much faster than the electron's momentum relaxation time due to electron-phonon interactions [18]. In the case of graphene, the relaxation time of the G peak pulsation is  $\sim 3$  fs, which is much smaller than typical electron-momentum relaxation time due to impurity, electron-electron and electron-phonon scatterings. Thus, excited electrons have no enough time to relax into the adiabatic ground state (Fig 2.7(c)). Therefore, electrons and phonons are strongly coupled, resulting in generating a strong G band frequency dependence on doping. The peak position and the intensity of the G' band also are changed by doping. However, the G' peak shows a different response to changes in the hole and electron concentrations; less sensitive than those of G peak due to no correlation with the non-adiabatic effects.

Figure 2.6. (a) Electronic structure of graphene: (up) undoped graphene (down) p-type doped graphene (b) G band energy (squares) and G band width (circles) as function of gate voltage and charge density [20].

Figure 2.7. (a) Bands of perfect crystal; Bands in the presence of an  $E_{2g}$  lattice distortion within (b) ABO (c) non-adiabatic (d) Atomic pattern of the  $E_{2g}$  phonon [18].

## 2.2.4 Raman spectrum in strained graphene

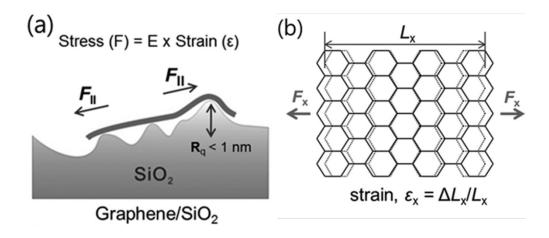

Graphene is mostly used as a form attached to a substrate. Then stain can be induced after transferring exfoliated or CVD graphene to substrates or growing epitaxial graphene on SiC substrates. The graphene on SiC substrate grown epitaxially at temperatures above  $1100 \,^{\circ}\text{C}$  exhibits compressive strain ( $\epsilon$ ) of around -1% at room temperature [21]. The graphene on SiO<sub>2</sub> substrates undergoes significant structural deformation with corrugation-induced strain at annealing temperature of 300  $^{\circ}\text{C}$  [13]. Even graphene on SiO<sub>2</sub> substrates without annealing process is deformed due to strong adhesion with undulating substrates (Fig 2.8(a)) [13].  $\epsilon$  is defined as a relatively stretched or compressed length with applied stress to uniaxial direction, with  $\epsilon > 0$  for tensile and  $\epsilon < 0$  for compressive strain (Fig 2.8(b)). The electronic band structure is changed by strain in graphene, resulting in change of the D, G and G' peak positions in Raman spectrum. Generally, phonon frequency is decreased with increase of tensile strain. On the other hand, phonon frequency is increased under compressive strain. As a result, the frequency of Raman peak is linearly changed with biaxial strain as shown in Fig 2.8(c) [22].

Figure 2.8. (a) Deformation of graphene on  $SiO_2$  (b) Graphene lattice structure deformed by strain (c) D, G, 2D (G') peaks plotted as a function of the biaxial strain  $\varepsilon_{\parallel}$  [22].

#### 2.2.5 Separation of the impacts from charge doping and strain in graphene

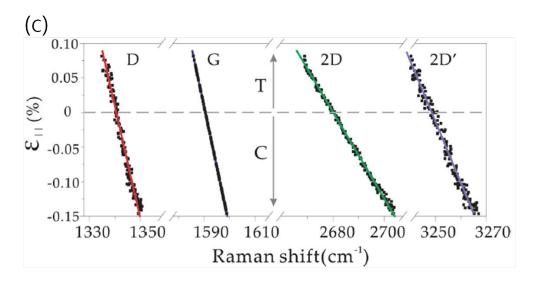

As stated above, lattice vibrations in graphene are affected by various parameters, such as doping and strain, with high sensitivity. For this reason, Raman spectroscopy is widely used to measure the graphene's various properties with high sensitivity. The challenge, however, is that the phonon frequencies react simultaneously with various parameters. In particular, Raman frequencies of  $G(\omega_G)$  and  $G'(\omega_G)$  band, the most widely used ones, are dependent on both extra charges and strain as described above. Thus, the bimodal sensitivity of  $\omega_G$  and  $\omega_G$  makes it difficult to independently determine either strain or charge density for quantitative interpretation.

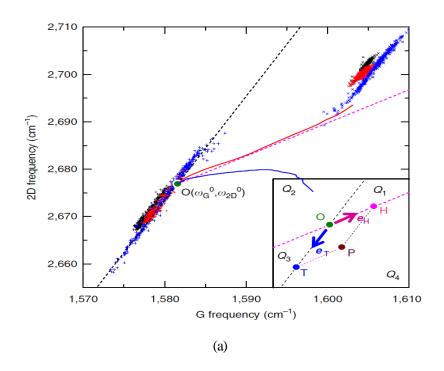

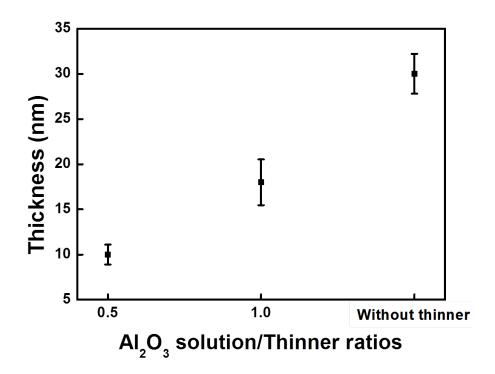

Recently, Lee *et al.* has reported that the effects of strain and charges can be separated from each other in terms of a correlation analysis of the two modes. It is based on the fact that the fractional variations in G and G' peak position caused by changing n (charge carrier concentration) are quite different from that is due to  $\varepsilon$  (strain) [11]. Lee *et al.*, set the G and G' peak positions ( $\omega_G^0$ ,  $\omega_G^0$ ) of a suspended graphene as the origin O of the  $\omega_G$  versus  $\omega_{G'}$  plot because the suspended graphene can be

viewed as nearly charge neutral and strain free (Fig 2.9(a)). In Figure 2.9 (b), the magenta dashed line is a linear fit obtained from a strain-free graphene with various hole concentrations. The blue dashed lines, drawn parallel to this line, therefore represent equi-strain lines. The hole doping induced by electrical gating leads to a quasi-linearity,  $(\Delta \omega_{G}/\Delta \omega_{G})_{n}^{\text{hole}} = 0.70 \pm 0.05$ , using two papers reported by the same group [23,24]. The black dashed line represents a theoretical prediction for a charge-neutral graphene under randomly oriented uniaxial stresses. The red solid lines, drawn parallel to this line, therefore represent equi-hole-concentration lines.  $(\Delta \omega_{G}/\Delta \omega_{G})\epsilon$  depends on the direction of the strain with respect to the crystallographic axes of graphene. G and G' mode of graphene under the stress splits into G' (G'') and G<sup>+</sup> (G'<sup>+</sup>) depending on the zigzag and arm-chair directions. While  $(\Delta \omega_{G}/\Delta \omega_{G})\epsilon$  and  $(\Delta \omega_{G}/\Delta \omega_{G})\epsilon$  of zigzag directions are 2.05 and 2.00,  $(\Delta \omega_{G}/\Delta \omega_{G})\epsilon$  and  $(\Delta \omega_{G}/\Delta \omega_{G})\epsilon$  of arm-chair directions are 1.89 and 3.00.  $(\Delta \omega_{G}/\Delta \omega_{G})\epsilon$ . For the zigzag and arm-chair directions, the average is obtained as 2.02 and 2.44, respectively. As a result, we speculate  $(\Delta \omega_{G}/\Delta \omega_{G})$  along any direction between the zigzag and arm-chair axes lie in the range 2.02-2.44. This value is in agreement with 2.2  $\pm$  0.2 obtained from experiment. This analysis is useful to separate the effects of strain and excess charges in graphene materials and devices.

In this work, we use this analysis to be more quantitative on doping and strain in graphene during formation of gate dielectric.

Figure 2.9. (a) Correlation between the frequencies of the G and G' (2D) Raman modes of graphene. (b) The theoretical and experimental trajectories of  $(\omega_G, \omega_{G'})$  affected by hole concentration and strain.

## 2.3 Device Fabrication

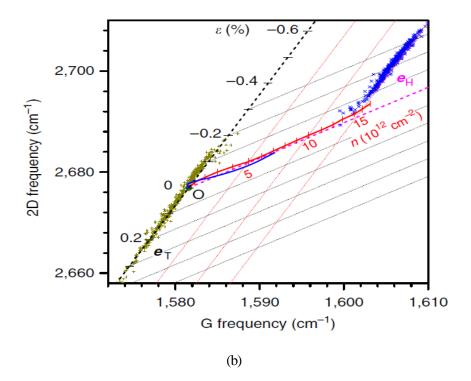

Fabrication sequence of dielectric formation on graphene and MIM (Metal-Insulator-Metal) capacitor is illustrated in Figure 2.10.

Figure 2.10. Fabrication sequences of dielectric formation on graphene and MIM capacitor.

Graphene layer was prepared by transferring a flake from kish graphite onto a Si substrate covered with a 90 nm-thick SiO<sub>2</sub> layer. In prior to the spin-coating of the Al<sub>2</sub>O<sub>3</sub> precursor liquid, part of the samples experienced a deposition of an ultrathin (~2 nm) Al layer (Experiment 3). This is to form an initial natural oxide layer (seeding layer) on graphene. The Al<sub>2</sub>O<sub>3</sub> precursor solution for the sol-gel method was prepared by mixing aluminum isopropoxide (Kojundo Chemical Laboratory Co., Ltd.) with xylenes and thinner. The concentration of the Al isopropoxide was 0.4 mol/L. The spincoating was conducted at a rotation speed of 4000 rpm for 20 s at room temperature. Part of the samples were then exposed to an oxygen plasma for 2 min at 30 W operated at 4 Pa (Experiment 2, 3). Samples were finally annealed at 200, 250, and 300 °C in air for 1, 2, and 3 hours (PDA). Damages [25], dopings [18], and strains [26] of graphene induced during the dielectric film formation were characterized by Raman scattering spectroscopy. Dielectric properties of the solution-processed Al<sub>2</sub>O<sub>3</sub> were evaluated by forming a metal-insulator-metal (MIM) capacitor on top of a SiO<sub>2</sub>-covered Si substrates (inset of Fig. 1). Both the top electrode of Al (150 nm) and the bottom electrode of Au (100 nm) were deposited by using an e-beam evaporator. The thickness of the Al<sub>2</sub>O<sub>3</sub> layers was measured by using spectroscopic ellipsometry. Electrical characteristics were measured at room temperature in the air ambient using Agilent B1500 semiconductor parameter analyzer.

## 2.4 Results and Discussion

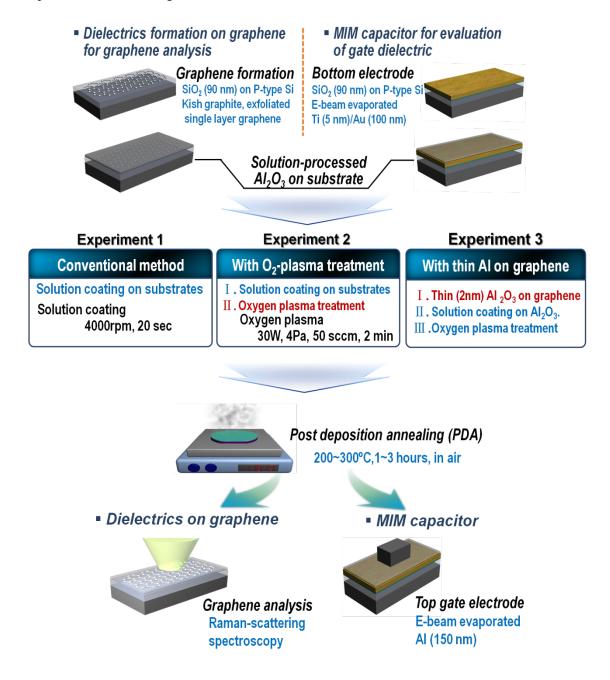

Figure 2.11 shows the thickness of solution-processed gate dielectrics formed at 250 °C PDA as a function of Al<sub>2</sub>O<sub>3</sub> solution/thinner ratios. After PDA at 250 °C, thickness of solution-processed gate dielectrics formed by only Al<sub>2</sub>O<sub>3</sub> solution is almost 30 nm. However, the thickness of gate dielectrics was decreased with increase of amount of thinner, 18, 10 nm at 1, 0.5 of Al<sub>2</sub>O<sub>3</sub> solution/thinner ratios, respectively. However, a formed solution, at Al<sub>2</sub>O<sub>3</sub> solution/thinner ratio of 0.3, couldn't deposit on graphene. We carried out to deposit on graphene using solution-processed gate dielectric of 10 nm thick.

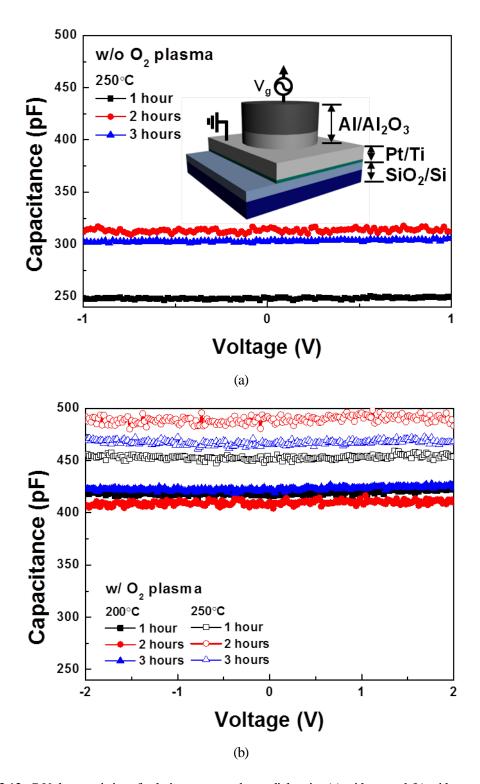

Figure 2.12 shows the capacitance-voltage (*C-V*) characteristics of the solution-processed Al<sub>2</sub>O<sub>3</sub> with and without oxygen plasma treatment, obtained in the high frequency (1MHz) regime using a MIM structure. The MIM structure is shown in the inset of Fig. 2.12 (a). As shown in the figure 2.12(a), the capacitances of the samples without the oxygen plasma treatments after 1, 2 and 3 hours PDA at 250 °C are 200, 300 and 315 pF, respectively. Since these values are insufficient for a FET operation, we decided to add post-coating oxygen-plasma treatment to accelerate the oxidation reactions at low temperatures. With the oxygen plasma treatment, a high capacitance of 400 pF or more has been obtained at even lower temperature of 200 °C. At 250 °C, the capacitance even exceeds 450 pF (Fig. 2.12 (b)).

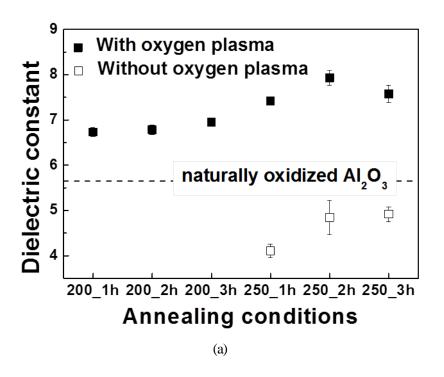

Figure 2.13 (a) shows the dielectric constants of the solution-processed Al<sub>2</sub>O<sub>3</sub>, obtained from a *C-V* measurement operated in the high frequency (1 MHz) regime using the MIM structure. The thickness of the Al<sub>2</sub>O<sub>3</sub> layer is 10 nm. The dielectric constants of the solution-processed Al<sub>2</sub>O<sub>3</sub> (open squares), however, fall far below that of naturally oxidized Al<sub>2</sub>O<sub>3</sub> even after a 3h PDA at 250 °C. With the oxygen plasma treatment (solid squares), on the other hand, the dielectric constant as high as ~8.0 is obtained after a PDA at 250 °C for 2 hours. It should be noted that this value is comparable to that of ALD-grown, thin Al<sub>2</sub>O<sub>3</sub> dielectric layer (7-9) [27] and is much higher than that of naturally

oxidized  $Al_2O_3$  [28]. The mechanism of this oxygen-plasma treatment will be discussed at the end of this chapter. To test the breakdown properties, current density (J) - voltage (V) characteristics have been obtained (Fig. 2.13 (b)). All samples are processed with the post-coating oxygen plasma treatment as well as with PDA at 200 and 250 °C. The samples annealed at 250 °C showed markedly lower leakage currents ( $<5\times10^9$  A/cm² at 1MV/cm) and higher breakdown fields (3.5 MV/cm) than those annealed at 200 °C. These results indicate that the oxygen plasma treatment is very effective in improving the electrical characteristics of solution-processed gate dielectrics.

Figure 2.11. Thickness of solution-processed gate dielectrics formed at 250  $^{\circ}$ C PDA as a function of Al<sub>2</sub>O<sub>3</sub> solution/thinner ratios.

Figure 2.12. *C-V* characteristics of solution-processed gate dielectrics (a) without and (b) with oxygen plasma treatment.

Figure 2.13. (a) Dielectric constant, as determined from C-V measurement, of the  $Al_2O_3$  film with (solid squares) and without (open squares) oxygen plasma treatments as a function of the PDA temperature and time. (b) J-V characteristics of the  $Al_2O_3$  MIM capacitor with oxygen plasma treatment.

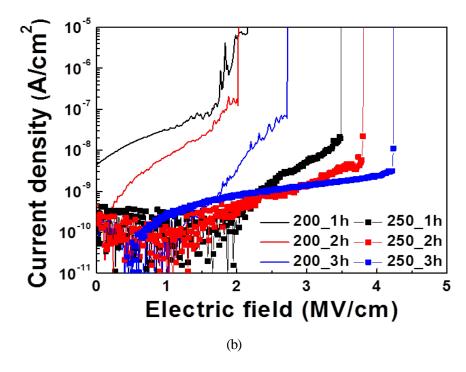

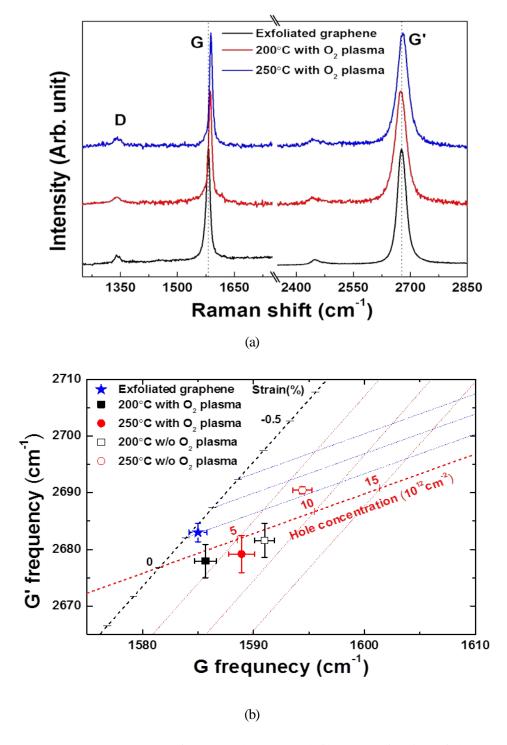

Although the dielectric and the breakdown properties of the dielectrics fabricated with solution/oxygen-plasma method seem quite promising, the doping levels are not yet ideal. Fig. 2.14 (a) shows Raman spectra of the samples annealed at 200 and 250°C for 2 hours after the oxygen plasma treatment, compared with that of exfoliated graphene. The main features of the spectrum, i.e. the positions of the D and G' peaks as well as the intensity of the D peak, are almost the same among the three samples. The only difference can be found in the G peak position, which noticeably blue-shifts with the increasing PDA temperature. A blue shift of the G band, in the absence of the G'-band shift, indicates a p-type doping [23]. The G band position is however a function not only of doping but also of strain. In the case of strain, the G' peak also shows a shift [11]. We have therefore plotted in Fig. 2.14 (b) the position of the G' peak against that of the G peak, both of which are known to be expressed by linear combinations of both doping and strain levels in graphene [11]. The magenta dashed line is a linear fit obtained from a strain-free graphene for various hole concentrations [24]. The blue dashed lines, drawn parallel to this line, therefore represent equi-strain lines. The black dashed line represents a theoretical prediction for a charge-neutral graphene under randomly oriented uniaxial stresses [29]. The red solid lines, drawn parallel to this line, therefore represent equi-holeconcentration lines. For oxygen-plasma-treated samples shown in solid symbols, the hole concentration increases with increasing PDA temperature, from  $3\times10^{12}$  to  $6\times10^{12}$  cm<sup>-2</sup>. Samples without the oxygen-plasma treatment shown in open symbols, on the other hand, shows a strong holedoping up to  $7\times10^{12}$  cm<sup>-2</sup>.

As we have seen, the solution-processed dielectric film with the oxygen plasma treatment shows excellent dielectric properties as well as lower hole dopings. The hole doping levels of  $3-6\times10^{12}$  cm<sup>-2</sup>, however, are still higher than that of exfoliated graphene ( $1\times10^{12}$  cm<sup>-2</sup>). Since dopings sharply deteriorate the carrier mobility of graphene channel [30] we need to decrease the doping to even lower levels. Our working hypothesis here is that the p-type doping should originate from oxygen-related

species adsorbing on graphene before the gate-oxide deposition. Pirkle et al. [30] have recently demonstrated that a deposited Al layer on graphene reacts with such oxygen-related ad-species on graphene, resulting in the formation of AlO<sub>x</sub> at the Al/graphene interface. Moreover, previous studies of Al thermal oxidation [32] show that the Al<sub>2</sub>O<sub>3</sub> thickness on Al saturates at ~2 nm or less for oxidation temperatures lower than 300 °C. These findings suggest that an ultrathin (~2 nm) layer of Al may most effectively consume all the oxygen-related ad-species on graphene to become AlO<sub>x</sub>. We have therefore decided to investigate the impacts of the natural oxide insertion, in prior to the solutionprocess formation of Al<sub>2</sub>O<sub>3</sub>, on the p-type doping in graphene. Figure 2.15 (a) shows the Raman spectra. The close-up of the D peak indicates that the D-peak rarely appears up to 250 °C regardless of the PDA time. At 300 °C the D peak markedly appears, indicating onset of damages. The G and G' peaks for 200- and 250 °C-annealed samples concurrently show a slight red shift with the PDA time. For the 300 °C-annealed sample, on the other hand, blue shifts are observed for both G and G' peaks. To be more quantitative, we have again plotted the G' peak position against the G peak position in Fig. 2.15 (b). The samples annealed at 200 and 250 °C are located in the vicinity of the charge neutral line, similar to suspended graphene [33]. High carrier mobilities can therefore be expected for the graphene under these dielectrics. The samples annealed at 300 °C, on the other hand, are strongly hole-doped up to  $5\times10^{12}$  cm<sup>-2</sup> or more. This can be related to onset of oxygen penetration to graphene through thinner portions and/or pin-holes of the Al natural oxide layer having substantial surface roughness (~1.2 nm). This point will be discussed later. Based on these results, we propose a modified solution process for the gate dielectrics on graphene. The process consists of initial formation of natural oxide of Al (seeding layer), solution-process of Al<sub>2</sub>O<sub>3</sub>, oxygen plasma treatment, and PDA at 250 °C.

Figure 2.14. (a) Raman spectrum of oxygen-plasma-treated films as a function of the PDA temperature. (b) G' peak position versus G peak position of the films with (solid squares) and without (open squares) oxygen plasma treatment for several PDA temperatures.

Figure 2.15. (a) Raman spectrum of  $Al_2O_3$  on graphene with initial insertion of natural oxide of Al. (b) G' peak position versus G peak position as a function of the PDA temperature and time for  $Al_2O_3$  on graphene with initial insertion of thin Al layer and with oxygen plasma treatment.

Figure 2.16 shows the AFM images of the samples after deposition of (a) Al (2 nm) thin film and (b) the solution-processed Al<sub>2</sub>O<sub>3</sub> films on the Al (2 nm) thin film with PDA at 250 °C, both on graphene. In Fig 2.16 (a), the surface consists of Al clusters and the RMS (Root Mean Square) surface roughness is as large as 1.26 nm. In Fig. 2.16 (b), on the other hand, the RMS surface roughness of the solution-processed Al<sub>2</sub>O<sub>3</sub> is strongly reduced to 0.34 nm. Based on this observation, a possible mechanism for the betterment of the dielectric properties of the Al<sub>2</sub>O<sub>3</sub> film by use of the present modified solution-process method is discussed in Fig. 2.17. After the Al deposition and the spincoating, the cross-section of the layers may look like the one shown by the close-up image shown in (I). The Al thin layer is sandwiched by oxygen atoms from both sides: one from the organic components in the solution film from the top side and the other from the remnant oxygen-related adspecies on the graphene surface from the bottom side. Part of these oxygen-related species can react with the Al film to form AlOx. When this spin-coated film is exposed to the oxygen plasma (II), the active oxygen radicals in the plasma will react with the precursor molecules in the spin-coated film, commencing the formation of Al<sub>2</sub>O<sub>3</sub> (III). During PDA at 250 °C, the oxygen species in the solutionprocessed precursor layer may diffuse into Al thin film, but the lack of thermal energy, as depicted by a thinner saturating oxide thickness (~0.5 nm) of Al at this temperature [32], may impede further diffusion of oxygen-related species to graphene. When the annealing temperature is increased to 300 °C, however, the higher thermal energy of the oxygen species, as indicated by a thicker saturating oxide thickness (~1.0 nm) of Al at this temperature [32], will allow their diffusion to graphene surface. Thinnest portion of the Al layer as well as pin-holes are suggested as a possible diffusion path to graphene. This accelerated diffusion of oxygen-species to graphene accounts for the observed doping and defects in graphene (IV). Without assist of this oxygen plasma, on the other hand, higher PDA temperatures are required to remove the organic fragments, which will drive onset of doping, strain, and mobility degradation of graphene [30,34].

Fig 2.16. AFM images of (a) Al (2 nm) deposited film on graphene and of (b) solution-processed  $Al_2O_3$  film on Al (2 nm) with oxygen plasma and PDA at 250 °C.

Fig 2.17. Schematic of the mechanism for the oxygen plasma growth for solution-processed Al<sub>2</sub>O<sub>3</sub>.

# 2.5 Conclusion

Based on a solution-process method, we have succeeded in fabrication of a gate dielectric Al<sub>2</sub>O<sub>3</sub> thin film on graphene with a sufficiently high quality. We propose a modified solution-process method, which consists of initial formation of ultrathin Al natural oxide, spin-coating of Al<sub>2</sub>O<sub>3</sub> precursor liquid, oxygen plasma treatment, and PDA. It was found that the PDA at 250°C for 2 hours gives a minimum doping and strain to graphene and a highest dielectric constant to Al<sub>2</sub>O<sub>3</sub>. Although this study was focused on minimizing the doping and strain in graphene during the gate-stack process, the strongly temperature-dependent doping found in this study can be utilized in controlling the threshold voltage of GFETs.

# Reference

- [1] P. Balk: The Si-SiO<sub>2</sub> System, ed. P. Balk (Elsevier, Amsterdam, 1988) pp.1.

- [2] J. F. Verwey, E. A. Amerasekera and J. Bisschop, Rep. Prog. Phys. **53**, 1297 (1990).

- [3] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Science 306, 666 (2004).

- [4] K. I. Bolotin, K. J. Sikes, Z. Jiang, M. Klima, G. Fudenberg, J. Hone, P. Kim, H. L. Stromer, Solid State Communications 146, 351 (2008).

- [5] F. Schwierz, Nat. Nanotechnol. 5, 487 (2010).

- [6] F. Schedin, A. K. Geim, S. V. Morozov, E. W. Hill, P. Blake, M. I. Katsnelson, and K. S. Novoselov, Nat. Mater. 6, 652 (2007).

- [7] Ph. Avouris, Nano Lett. 10, 4285 (2010).

- [8] B. Lee, S. Y. Park, H. C. Kim, K. J. Cho, E. M. Vogel, M. J. Kim, R. M. Wallace, and J. Kim, Appl. Phys. Lett. 92, 203102 (2008).

- [9] S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, Appl. Phys. Lett. 94, 062107 (2009).

- [10] X. Lu, H. Huang, N. Nemchuk, and R. S. Ruoff, Appl. Phys. Lett. **75**, 193 (1999).

- [11] J. E. Lee, G. Ahn, J. Shim, Y. S. Lee, and S. Ryu, Nat. Comm. 3, 1024 (2012).

- [12] S. M. Song, and B. J. Cho, Nanotechnology **21**, 335706 (2010).

- [13] S. Ryu, L. Liu, S. Berciaud, Y. J. Yu, H. Liu, P. Kim, G. W. Flynn, and L. E. Brus, Nano Lett. 10, 4994 (2010).

- [14] A. C. Ferrari, J. C. Meyer, V. Scardaci, C. Casiraghi, M. Lazzeri, F. Mauri, S. Piscance, D. Jiang, K. S. Novoselov, S. Roth, and A. K. Geim, Physical Review Letters 97, 187401 (2006).

- [15] L. M. Malard, M. A. Pimenta, G. Dresselhaus, and M. S. Dresslhaus, Physics Reports 473, 51 (2009).

- [16] R. Beams, L. G. Cancado, and L. Novotny, Journal of Physics: Condensed Matter 27, 083002 (2015).

- [17] S. D. Sarma, S. Adam, E. H. Hwang, and E. Rossi, Reviews of Modern Physics 83, 407 (2011).

- [18] S. Pisana, M. Lazzeri, C. Casiraghi, K. S. Novoselov, A. K. Geim, A. C. Ferrari, and F. Mauri, Nat. mater. 6, 198 (2007).

- [19] R. Bauernschmitt, and R. Ahlrichs, Chemical Physics Letters 256, 454 (1996).

- [20] J. Yan, Y. Zhang, P. Kim, and A. Pinczuk, Physical Review Letters 98, 166802 (2007).

- [21] D. S. Lee, C. Riedl, B. Kraub, K. Klitzing, U. Starke, and J. H. Smet, Nano Letters 8, 4320 (2008).

- [22] F. Ding, H. Ji, Y. Chen, A. Herklotz, K. Dorr, Y. Mei, A. Rastelli, and O. G. Schmidt, Nano Letters 10, 3453 (2010).

- [23] A. Das, S. Pisana, B. Chakraborty, S. Piscanec, S. K. Saha, U. V. Wagghmare, K. S. novoselov, H. R. Krishnamurthy, A. K. Geim, A. C. Ferrari, and A. K. Sood, Nat. Naotechnol. 3, 210 (2008).

- [24] A. Das, B. Chakraborty, S. Piscanec, S. Pisana, A. K. Sood, and A. C. Ferrari, Phys. Rev. B **79**, 155417 (2009).

- [25] L. G. Cancado, A. Jorio, E. M. Ferreira, F. Stavale, C. A. Achete, R. B. Capaz, M. V. O. Moutinho, A. Lombardo, T. S. Kulmala, and A. C. Ferrari, Nano lett. 11, 3190 (2011).

- [26] T. M. G Mohiuddin, A. Lombardo, R. R. Nair, A. Bonetti, G. Savini, R. Jalil, N. Bonini, D. M. Basko, C. Galiotis, N. Marzari, K. S. Novoselov, A. K. Geim, and A. C. Ferrari, Phys. Rev. B 79, 205433 (2009).

- [27] S. M. George, Chem. Rev. **110**, 111 (2010).

- [28] C. C. Lu, Y. C. Lin, C. H. Yeh, J. C. Huang, and P. W. Chiu, ACS nano, 6, 4469 (2012).

- [29] D. Yoon, Y. W. Son, and H. Cheong, Phys. Rev. Lett. **106**, 155502 (2011).

- [30] J. H. Chen, C. Jang, S. Adam, M. S. Fuhrer, E. D. Williams, and M. Ishigami, Nat. Phys. 4, 377

(2008).

- [31] A. Pirkle, R. M. Wallace, and L. Colombo, Appl. Phys. Lett. 95, 133106 (2009).

- [32] L. P. H. Jeurgens, W. G. Sloof, F. D. Tichelaar, and E. J. Mittemeijer, J. Appl. Phys. **92**, 1649 (2002).

- [33] S. Berciaud, S. Ryu, L. E. Brus, and T. F. Heinz, Nano Lett. 9, 346 (2009).

- [34] J. H. Chen, W. G. Cullen, C. Jang, M. S. Fuhrer, and E. D. Williams, Phys. Rev. Lett. **102**, 236805 (2009).

# Electrical properties of GFETs with solution-processed top-gate

# 3.1 Introduction

Graphene has attracted much attention as a new channel material for next generation electronic device applications due its extremely high mobility and electric-field induced carrier density modulation. For these reasons, remarkable development has been made on graphene-based electronic devices in the past few years. Actual graphene FETs (GFETs), however, suffer significant degradation of pristine properties due to impurities [1], defects [2], dielectric environment [3,4] in graphene sheet during the fabrication process of GFETs.

As stated above, it was reported that the mobility significantly decreases and the gate voltage of the minimum conductivity (Dirac point) shifts to more negative values with increase of potassium doping, which means increase of charged impurities (Fig. 3.1(a)). As the defect density increases, the mobility also significantly decreases and the reduction of  $\sigma_{min}$  by doping is roughly proportional to the reduction of the mobility (Fig. 3.1 (b)). Furthermore, it was reported that charge carrier mobility is dependent on dielectric constant surrounding the graphene sheet. There are two competing mechanisms. The impurity scattering can be strongly suppressed by using high-k dielectrics, while increasing the phonon scattering. By using low-k dielectrics, on the contrary, impurity scattering is dominant but the phonon scattering is lower than that of high-k dielectrics. The limitation of the

carrier mobilities ( $\sim 10^4$  cm<sup>2</sup>/Vs) is attributed to the trade-off between the impurity scattering and the phonon scattering as shown Fig. 3.2 [3]. The gate dielectrics process in GFETs, in this respect, is required to minimize the defects and the doping in graphene during the gate dielectrics formation and to choose the dielectric materials with an appropriate dielectric constant.

In the previous chapter, we discussed the possibility of applying the solution-processed gate dielectrics in GFETs. We found, by using Raman-scattering spectroscopy, that defects, dopings, and strains are introduced in graphene during formation of gate dielectric films. It was however shown that the excellent electrical characteristics with minimum defects, dopings, and strains in graphene can be obtained by inserting an initial natural oxide seeding layer onto graphene, by adding an oxygen plasma treatment, and by tuning the PDA temperature. With the high suppression of hole doping and defects, we now have good reasons to expect high carrier mobility [5,6]. Few studies, however, have been made on these solution-processed gate dielectrics to fabricate GFETs [7]. In particular, no studies have been reported on the top-gated GFETs (TG-GFETs) with the solution-processed gate dielectrics.

In this chapter, fabrication of the TG-GFETs (Fig 3.1) with the solution-processed gate dielectrics will be described. It will be demonstrated experimentally that the Dirac point shift (doping) is closely related with decrease of the intrinsic carrier mobility in graphene.