ぱく ぐんほ 氏 名 君昊 Goon-Ho Park 朴 授 与 学 位 博士 (工学) 学位授与年月日 平成27年3月25日 学位授与の根拠法規 学位規則第4条第1項 研究科, 専攻の名称 東北大学大学院工学研究科(博士課程)電子工学専攻 位論文題目 Studies on Graphene Field Effect Transistors: Solution-Processed Gate Dielectrics and UV-Ozone-Processed Contact Resistance グラフェン電界効果トランジスタに関する研究―溶液法によるゲート絶縁膜形 成とUVオゾン法による接触抵抗-教 指 員 東北大学教授 末光 **追希** 審查委員 主查 末光 東北大学准教授 哲也 眞希 末光 東北大学教授 尾辻 泰 東北大学准教授 吹留 博-東北大学教授 佐藤 茂雄 客員教授 長澤 弘幸

## 論 文 内 容 要 旨

Graphene has attracted increasing attention as a strong candidate for the post-silicon channel material due to its exceptional physical, thermal, and electrical properties, such as ultrahigh carrier mobility, thermal and chemical stability, 2D structure and Si process compatible. This research has been focused on the betterment of the process and the design of graphene-based field-effect transistors (GFET) to optimize its performance. The following is the summary of each chapter.

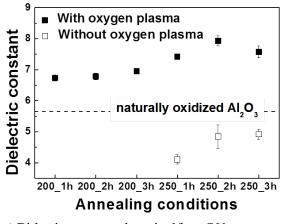

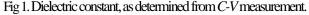

In chapter 2, based on a solution-process method, a gate dielectric  $Al_2O_3$  thin film was successfully fabricated on graphene with a sufficiently high quality. Based on a systematic characterization of the film, a modified solution-process method, which consists of initial formation of ultrathin Al natural oxide, spin-coating of  $Al_2O_3$  precursor liquid, oxygen plasma treatment, and PDA, has been proposed. It was found that the PDA at 250°C for 2 hours gives a minimum doping and strain to graphene (Fig. 1) and a highest dielectric constant to  $Al_2O_3$  (Fig. 2). A strongly temperature-dependent doping behavior was found to exist, which can be further utilized in controlling the threshold voltage of GFETs.

Fig 2. G' peak versus G peak position for Al<sub>2</sub>O<sub>3</sub> on graphene

In chapter 3, top-gate FETs with the gate dielectrics deposited by the modified solution method have been fabricated. The gate process consists of initial formation of a natural oxide layer of Al, spin-coating of the sol-gel precursor for  $Al_2O_3$ , the oxygen plasma treatment, and PDA. PDA at 250 °C was found ideal in achieving the high intrinsic carrier mobility ( $\sim$ 8400 cm<sup>2</sup>/Vs) in the PDA temperature range (200-300 °C) tested (Table. 1). With this high potential, the modified solution-processed gate dielectrics are quite promising for realizing high performance GFETs.

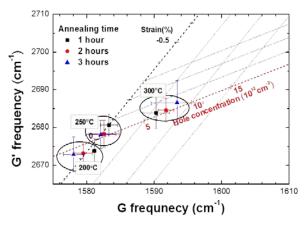

In chapter 4, UVO<sub>3</sub> treatment has been demonstrated to be quite effective in reducing the contact resistance, which is related to removal of the interfacial contaminations. The UVO<sub>3</sub> treatment after the photolithographic process is found quite effective in removing the PR residue without inducing substantial damages to graphene. As a result, the transconductance and the filed-effect mobility characteristics are remarkably improved by the UVO<sub>3</sub> treatment of 3 min. Finally, a low contact resistance ranging from 100 to  $400 \Omega$  µm was obtained (Fig. 3), which is comparable or less than the reported values made on the same material system. These results provide important insights for betterment of the GFET performance.

| PDA<br>(°C) | μ <sub>int</sub> electron<br>(cm²/Vs) | μ <sub>int</sub> hole<br>(cm²/Vs) | <b>n</b> <sub>0</sub> (cm <sup>-2</sup> ) |

|-------------|---------------------------------------|-----------------------------------|-------------------------------------------|

| 200         | 4850                                  | 4980                              | 3.5×10 <sup>11</sup>                      |

| 250         | 8430                                  | 8400                              | 2×10 <sup>11</sup>                        |

| 300         | -                                     | 2470                              | 1×10 <sup>12</sup>                        |

Table 1. Comparison of the intrinsic carrier mobilities and residual carrier concentration at various PDA temperatures.

Fig 3. Normalized contact resistance as a function of  $UVO_3$  treatment time in b ack-gated graphene FETs.

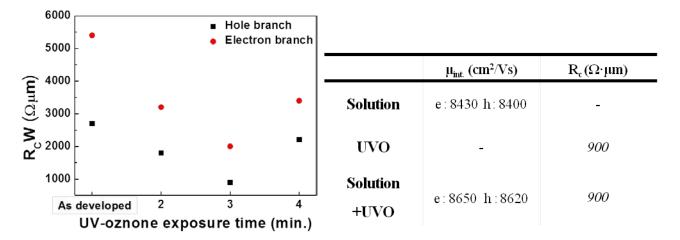

In chapter 5, TG-GFETs with overlapped S/D to gate structure and UVO<sub>3</sub>-treated contacts have been successfully fabricated. The UVO<sub>3</sub> treatment effectively eliminates the residual photoresists and hence reduces the contact resistance at the M/G junctions. Reduction of the access region can also minimize the total resistance. As a result, a relatively low contact resistance of 900  $\Omega$  µm (Fig. 4) is obtained for the TG-GFET. The ON-current ( $I_{on}$ ) is increased, and the field-effect mobility of 210 cm<sup>2</sup>/Vs was obtained. UVO<sub>3</sub> processed M/G contact and overlapped S/D to gate structure are quite promising for realizing high performance GFETs.

In chapter 6, GFETs integrating all the technologies developed in chapters 2-5 have been fabricated: the solution-processed gate dielectrics, the UVO<sub>3</sub>-treated contacts, and overlapped S/D to top-gate electrode. Highest transconductance and field-effect mobility, not achievable by the solution gate or the UVO<sub>3</sub>-treated contacts alone, have been

obtained. These high transport values are attributed to both the increase of the intrinsic mobility (due to solution gate) and the reduction of the contact resistance (Table. 2). It is therefore concluded that combination of solution-processed gate dielectric and UVO<sub>3</sub>-treated contacts, as well as overlapped S/D to top-gate, is quite promising for realizing high performance GFETs.

${

m Fig}$  4. Normalized contact resistance as a function of  ${

m UVO_3}$  exposure time in top-gated graphene FETs.

Table 2. Comparison of intrinsic mobility and contact resistance of fabricated device in the work

## 論文審査結果の要旨

高いキャリア移動度を有するグラフェンは、電界効果トランジスタ(FET)の次世代材料として幅広い注目を集めている。しかし今日のグラフェン FET(GFET)は、グラフェンの持つ高キャリア移動度をデバイス性能として十分に引き出し切れていない。著者は(1)ゲート絶縁膜堆積工程におけるグラフェンの品質劣化、(2)ソース・ドレイン電極の接触抵抗、(3)ゲート両端のアクセス抵抗の三者がGFET 性能を大幅に劣化させていることに注目し、これら課題の解決を図った。本論文は、その研究成果をまとめたもので、全文7章より成る。

## 第1章は序論である.

第2章では、薄膜トランジスタで広く用いられてきたゾル・ゲル溶液法を GFET 用 Al<sub>2</sub>O<sub>3</sub> ゲート絶縁 膜堆積に初めて適用した結果について述べている。同工程によって生じるグラフェンでの正孔ドーピング、歪発生、劣化をラマン分光法を用いて詳細に調べ、溶液スピンコート後に時間管理された酸素プラズマ処理を施すことで、グラフェンにおけるドーピング、歪発生、劣化を著しく抑制できることを見出した。同技術(以下「改良溶液法」)は GFET 用に特化した新しいゲート絶縁膜作製法として、きわめて高く評価される。

第3章では、第2章で開発した改良溶液法を用いて製作したトップゲート型 GFET の電気特性評価について述べている。高品質グラフェン膜を提供する最適ゲート絶縁膜成膜条件の時に GFET 電気特性も最大化され、そこから抽出されたキャリア移動度は電子移動度 8430 cm²/Vs, 正孔移動度 8400 cm²/Vs という、Si の5倍~20倍の値が得られることを明らかにしている。これは特筆すべき成果である。

第4章ではソース・ドレイン電極の接触抵抗低減の成果について述べている。フォトリソグラフィエ程を行った後に時間管理された UV オゾン処理を適用することにより、レジスト残渣が除去され、かつグラフェン劣化の抑制されたグラフェン表面が得られることを報告し、その結果、Ni/グラフェンの接触抵抗が  $100\sim400~\Omega\mu m$  という、従来値の  $2~\Omega m$  という、で来値の  $2~\Omega m$  という、できない。

第5章は、第4章に述べた UV オゾン処理によって接触抵抗を、また新たに T 型ゲートの採用によってアクセス抵抗をそれぞれ最小化させて製作したトップゲート型 GFET の電気特性評価について述べている。得られた接触抵抗値 900  $\Omega$ µm はソース・ドレイン電極下のグラフェンにキャリアを電界誘起できないトップゲート型 GFET としては有意に低く、従来よりも 25%以上低減されている。これは顕著な成果である。

第6章は、第2~第5章で開発したゲート絶縁膜堆積法と接触・アクセス抵抗低減法を組み合わせて製作したトップゲート型 GFET の電気特性評価について述べている。電子移動度 8650 cm²/Vs, 正孔移動度 8620 cm²/Vs という高移動度を実現することに成功し、改良溶液法、UV オゾン処理、T型トップゲートの3技術の組合せが GFET 電気特性の向上にきわめて有効であることを明らかにしている。これは特筆すべき成果である。

## 第7章は結論である.

以上要するに本論文は、GFET の性能劣化の原因となっていた(1)ゲート絶縁膜堆積工程におけるグラフェン劣化、(2)ソース・ドレイン電極の接触抵抗、(3)ゲート周辺のアクセス抵抗を、(1)改良溶液法の開発、(2)UVオゾン処理の採用、(3)T型ゲートの採用によって解決した成果をとりまとめたものであり、電子工学及び半導体デバイス工学の発展に寄与するところが少なくない。よって、本論文は博士(工学)の学位論文として合格と認める.