# Characterization of spin-orbit torque-controlled synapse device for artificial neural network applications

William A. Borders<sup>1</sup>, Shunsuke Fukami<sup>1,2,3,4,5,6\*</sup>, and Hideo Ohno<sup>1,2,3,4,5,6</sup>

<sup>1</sup>Laboratory for Nanoelectronics and Spintronics, Research Institute of Electrical Communication, Tohoku University, Sendai 980-8577, Japan <sup>2</sup>Center for Spintronics Integrated Systems, Tohoku University, Sendai 980-8577, Japan <sup>3</sup>Center for Innovative Integrated Electronics Systems, Tohoku University, Sendai 980-0845, Japan

<sup>4</sup>Center for Spintronics Research Network, Tohoku University, Sendai 980-8577, Japan <sup>5</sup>Center for Science and Innovation in Spintronics (Core Research Cluster), Tohoku University, Sendai 980-8577, Japan

<sup>6</sup>WPI-Advanced Institute for Materials Research, Tohoku University, Sendai 980-8577, Japan

\*E-mail: s-fukami@riec.tohoku.ac.jp

In recent years, there has been an increasing need for dedicated devices that act as components of the brain for use in non-von Neumann-based architectures known as artificial neural networks (ANNs). Furthermore, to transition from the large, power-consuming supercomputer paradigm used to complete brain like tasks, such as pattern recognition, to a "wearable" edge-computing-based artificial intelligence (AI) paradigm, compact and efficient hardware is required. In this report, we describe one such approach towards hardware-based ANNs using recently reported spintronics technology. We give a systematic explanation on a procedure of an ANN-based associative memory operation using spin-orbit torque-controlled devices. On the basis of previously obtained results, we then elaborate on the specific roles and requirements of spintronics devices in the demonstration system. We also describe several challenges regarding efficient and reliable operation of the device sthat is clarified by additional measurements of endurance properties of the device as a function of operation current. The results indicate that limitation of the maximum operation current to prevent the decay of device properties provides negligible device-to-device variation after hundreds of iterations, allowing for a reliable associative memory operation.

# 1. Introduction

Research on developing artificial intelligence (AI) technology is a rapidly increasing field of interest for fabricating machines, devices, and large computing systems that can perform tasks such as high-performance pattern recognition and interpretation of ambiguous information that the human brain excels at. A recognizable trend in recent years has been seen that begins with implementing AI algorithms such as deep learning on CMOS-based, conventional von Neumann computing architecture<sup>1)</sup>. An architectural mismatch, however, arises when implementing algorithms suited for the parallel, asynchronous architecture of the brain on the sequential clock-driven von Neumann architecture. This mismatch leads to an overhaul in time and power consumption compared with the human brain. One solution is to implement CMOS technology onto a unique, non-von Neumann architecture, otherwise known as an artificial neural network (ANN)<sup>2-4)</sup>. This architecture models the processing centers of the brain (i.e. neurons) with the data centers connecting two neurons, synapses, to improve operation efficiency and brain likeness. However, CMOS technology on its own does not have dedicated hardware to represent the aspects of the brain. In large-cell-area ANNs, the large number of neurons used exponentially increases the number of required synapses, which in turn creates a need for systems with high density and high speeds. The paradigm known as 'edge computing' has recently arisen, which aims to deliver dedicated devices for representing synapses and neurons<sup>5-11</sup>). Spintronics technology is a contender to fit in such a paradigm owing to its capability to produce devices with nonvolatility, analogue-like behavior, and virtually infinite read/write endurance<sup>12-18)</sup>.

In this study, we give a systematic explanation regarding the procedure of an ANN-based associative memory operation<sup>19)</sup> and the role of spintronics devices<sup>20,21)</sup> as artificial synapses. The work utilizes the physical interaction at the interface of antiferromagnet (AFM) and ferromagnet (FM) layers to produce an analogue-like change in output resistance. This change is proportional to the perpendicular component of magnetization in the FM layer, which is switched by an exchange-bias field from the AFM layer<sup>22)</sup> and a current-induced torque known as the spin-orbit torque (SOT)<sup>23-25)</sup>. In the human brain, a synaptic junction weight evolves in an analogue-like manner, similarly to an SOT device, leading to the assumption that SOT devices can take on the role as dedicated synaptic devices in an ANN. We first briefly describe the previously reported results obtained using an SOT device as an artificial synapse in a proof-of-concept demonstration of the brain like associative memory operation. In this paper we explain in further detail how to teach devices to recognize patterns through an iterative learning process and then how to determine if the devices can reproduce the learned

patterns when the input to the system is noisy. In addition to an explanation of a previous report, we also include further device characterization and describe the challenges uncovered when implementing the devices under the current operation scheme and provide insights into improving the devices for realization in viable spintronics-based edge-computing technologies.

# 2. Experimental methods

### 2.1 SOT device preparation

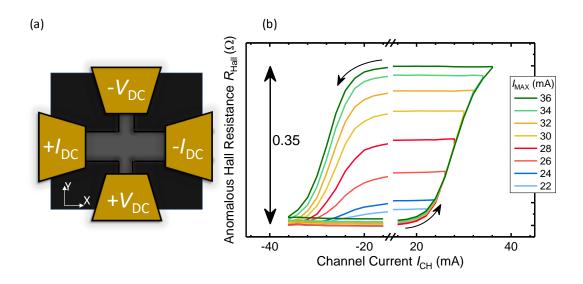

To effectively operate SOT devices, a proper device structure and a read out scheme is necessary. To fabricate the SOT devices, an AFM-FM stack is deposited on Si wafers by sputtering under zero magnetic fields. The structure of the film is, from the substrate side, Ta(3)/ Pt(2.2)/ PtMn(9.5)/ Pt(0.6)/ [Co(0.3)/Ni(0.6)]<sub>2</sub>/ Co(0.3)/ MgO(1)/ Ru(1) (in nm)<sup>26</sup>). The stacks are then fabricated into Hall bar devices with a 5-µm-wide channel by photolithography and Ar ion milling [Fig. 1(a)]. Cr/Au electrodes are then patterned to form electrical contacts. Hall bar devices are then annealed in a 1.2 T magnetic field along the - X-direction for 2 h at 300 °C to apply the exchange bias necessary for SOT switching. The anomalous Hall voltage  $V_{\text{Hall}}$  with respect to the DC channel current  $I_{\text{CH}}$  (read across the electrodes patterned in the Y-direction) is converted into an anomalous Hall resistance  $R_{\text{Hall}}$ , and plotted in Fig. 1(b). The analogue-like switching is seen by initializing the device with a *-I*<sub>CH</sub> magnitude and then sweeping  $I_{\text{CH}}$  towards various magnitudes of  $I_{\text{MAX}}$ . Regardless of the magnitude of  $I_{\text{MAX}}$ ,  $I_{\text{CH}}$  is reset to the same negative value after each iteration. The sweeping is carried out by sending a 0.3 s  $I_{\text{CH}}$  pulse in the X-direction and then applying a 0.1 s read current of 1 mA to read  $V_{\text{Hall}}$ .

### 2.2 Construction of ANN

In our previous work<sup>19</sup>, we implement the SOT devices as artificial synapses in a Hopfield model<sup>27)</sup>-based ANN for pattern recognition tests. This model is often considered comparable to a content-addressable memory where an input state with complete or incomplete portions of desired information is applied to a state space. The state space will then converge and output an energetically minimized stable state to represent the system. Conventional Hopfield models are used for forming a state space (later noted as the synaptic weight matrix) that will produce the desired stable state (later noted as block patterns). The discrete Hopfield model, similar to many ANNs, describes the input and output of the system with vectors, henceforth, named state vectors where each element in the vector represents a neuron in either the "ON"

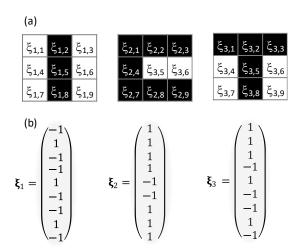

(1) or "OFF" (-1) states. We represent three  $3 \times 3$  block patterns with these state vectors [Figs 2(a) and 2(b)]; the values of 1 and(-1) corresponding to a black block and a white block, respectively. A  $3 \times 3$  block pattern provides a total of nine blocks; therefore, each state vector contains nine elements.

The Hopfield model is designed to determine the stable states of the system in response to a certain input using the following equation:

$$\mathbf{y} = \operatorname{sgn}(\mathbf{W}\mathbf{y} + \mathbf{b})$$

$$\operatorname{sgn}(x) = \begin{cases} +1 & \text{if } x > 0 \\ -1 & \text{if } x < 0 \end{cases},$$

(1)

where y represents the state vector, W represents the synaptic weight matrix, b represents a bias vector (= 0 in this study), and sgn() is the signum function. When an input is applied, Eq. (1) will iterate until the right side of equation produces a state vector identical to that on the left side of Eq. (1). The produced result is determined as a stable state vector. The representative synaptic weight matrix W of the system formed so that the desired three  $3\times3$  block patterns become stable states [Fig. 2(c)] is determined by

$$\mathbf{W} = \sum_{\mu=1}^{M} \mathbf{\xi}_{\mu} \mathbf{\xi}_{\mu}^{T} - M \cdot \mathbf{I}, \qquad (2)$$

where M denotes the number of patterns (= 3),  $\xi_{\mu}$  represents the state vector of the pattern  $\mu$  ( $\mu = 1, 2, 3$ ), T denoting the transpose operator, and I the identity matrix. As can be seen in Fig. 2(c), the values of W are symmetric across the diagonal. This translates to 36 unique synaptic weights, or rather 36 unique SOT devices. Furthermore, there are four distinct values shown: -3, -1, 1, and 3. To protect against a misinterpretation of the state, a maximum of four  $R_{\text{Hall}}$  levels are designated to represented the four snyaptic weights used.

#### 2.3 Associative memory demonstration

To demonstrate the associative memory capabilities of analogue SOT devices, the system is first taught the three  $3\times3$  patterns through an iterative learning process. To do so, there are three types of vectors that are necessary: the memorized vectors, which are stored in the personal computer (PC) and hold the ideal state vector values for "I", "C", and "T", the key vectors, which are the input vectors to the synaptic weight matrix, and the recalled vectors, which are the stable state vectors that the signum function has converged to. The learning process is performed by first measuring the  $R_{\text{Hall}}$ - $I_{\text{CH}}$  curves for each of the 36 devices and mapping four levels on the linear region (defined as the dynamic range) of the  $R_{\text{Hall}}$  curve to correspond to four synaptic weight levels. Each device's  $R_{\text{Hall}}$  is then changed with  $I_{\text{CH}}$ . For example, the  $R_{\text{Hall}}$  of SOT device #1 that is used to store  $W_{2,1}$  in **W** will be written with a value of  $I_{\text{CH}}$  corresponding to a synaptic weight of 1. After the writing phase, the  $R_{\text{Hall}}$  of each SOT device is read and mapped into synaptic weights to create a recalled **W**. At this point the key vectors are applied, one at a time to the recalled **W** as in Eq. (1) to produce one recalled vector  $\boldsymbol{\zeta}_{\mu}$  ( $\mu = 1, 2, 3$ ) for each pattern.

If any of the recalled vectors do not perfectly match the three state vectors stored in memory, the recalled **W** is not a representative synaptic weight matrix of  $\xi_{\mu}$ , or rather, the SOT devices have not successfully learned "I", "C", and "T", and each weight in **W** is adjusted according to<sup>28)</sup>

$$\Delta W = \sum_{\mu=1}^{M} \eta \left( \boldsymbol{\xi}_{\mu} \boldsymbol{\xi}_{\mu}^{T} - \boldsymbol{\zeta}_{\mu} \boldsymbol{\zeta}_{\mu}^{T} \right), \tag{3}$$

where  $\eta$  is a learning coefficient that determines the rate of learning. If the value is too high, the final change in **W** will result in a too vague weight matrix. If the value is too small, the system will require too many iterations of adjusting the synaptic weight. During the experiments,  $\eta$  is set to 0.005. The result of Eq. (3) is then applied to the current **W** by sending *I*<sub>CH</sub> to the SOT devices. At this point, the process is repeated until the recalled **W** produces stable state vectors identical to the memory vectors.

After the SOT devices have learned the patterns, the final recalled W is stored in memory to use in an associative memory operation. Noisy vectors are applied to the final recalled W. During the learning process, the key vectors were identical to the memory vectors; thus, each key vector now has a single element flipped (-1 to 1 or 1 to -1). The objective is to determine whether the W that the SOT devices converge to using the Hopfield model is capable of associating patterns, an important aspect of the human brain and pattern recognition. The associative memory operation goes through 100 trials before summarizing the results.

### 3. Results and discussion

#### 3.1 Associative memory operation

The SOT device array takes a maximum of 20 learning cycles to learn the three patterns, that is, the devices undergo at least several read/write cycles of their  $R_{\text{Hall}}$ . By applying an associative memory operation to the system, the synaptic weight matrix that the SOT devices learned can associate the memorized patterns from noisy inputs. This is seen by calculating the mean direction cosine (represented by the degree of agreement between the recalled and memorized patterns), which recovers to nearly the ideal value after applying the learning process. These results give one of few experimental demonstrations that spintronics devices

can be implemented in ANNs.

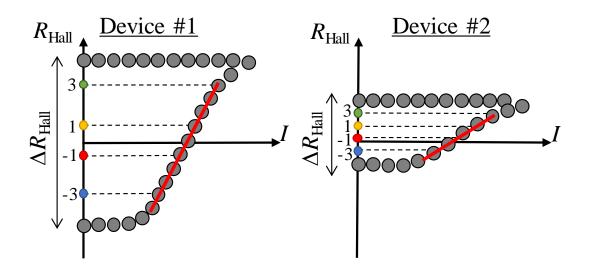

While the results of this proof-of-concept are very promising, to improve the efficiency and reliability of the system, the variation between devices must be reduced. A previous work<sup>19)</sup> shows in detail a histogram of the  $R_{\text{Hall}}$  of 36 SOT devices before and after the learning process. A distinct change in the distribution of levels can be seen, which demonstrates the capability of the device to learn patterns. However, the after-learning histogram shows deviation from the ideal histogram, which can be attributed to the variation the dynamic range of the  $R_{\text{Hall}}$ - $I_{\text{CH}}$  output characteristics. Furthermore, the reason why the direction cosine does not recover completely to the ideal value is also attributed to the variation of the dynamic range of the SOT devices. Figure 3 shows an example of  $R_{\text{Hall}}$ - $I_{\text{CH}}$ characteristics of two representative devices with different dynamic ranges, affecting the operation of the system. With a small dynamic range, there is a reduction in distinction between levels, where a small dynamic range may cause misinterpretation of the synaptic state.

During experimental measurements of the device  $R_{\text{Hall}}$ - $I_{\text{CH}}$  characteristics, the maximum switching amplitude  $\Delta R_{\text{Hall}}$  showed a larger difference than the switching amplitude after insertion into the demonstration circuit. Typically, such a change in switching amplitude is not expected, meaning that there is an altering effect during operation that is reducing the capabilities of the devices.

### 3.2 Study of device variation and reduced performance

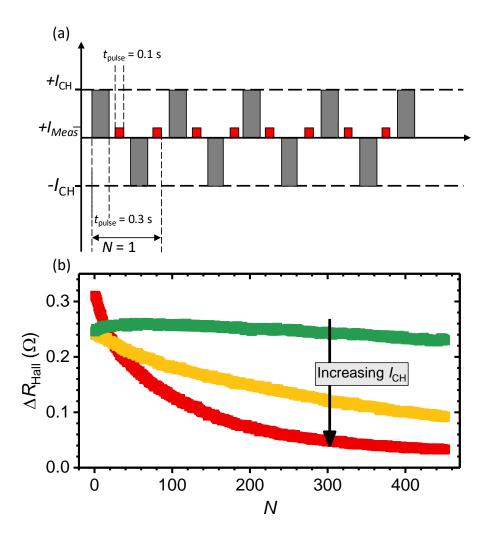

To understand more about the reason behind the large variation, and to find a way to improve the SOT devices for ANN applications, additional experiments were carried out. During the initial testing of the demonstration circuit, batch testing of the SOT devices was carried out to determine the average output characteristics of each device. The  $\Delta R_{\text{Hall}}$  of each device before the batch testing of 400 read/write cycles was observed to decrease in amplitude. After replicating the same devices, the devices are tested by applying a current pulse of  $-I_{\text{CH}}$ for 0.3 s to the device and measuring  $R_{\text{Hall}}$  with a 0.1-s 1-mA  $I_{\text{CH}}$  pulse. A current pulse  $+I_{\text{CH}}$ for 0.3 s is then applied and the  $R_{\text{Hall}}$  magnitude is measured. This process is repeated more than 400 times to represent the number of read/write cycles applied to the device during the associative memory operation [the measurement sequence is shown in Fig. 4(a)]. Figure 4(b) shows the resulting  $\Delta R_{\text{Hall}} = R_{\text{Hall}}^{+I_{\text{CH}}} - R_{\text{Hall}}^{-I_{\text{CH}}}$ .

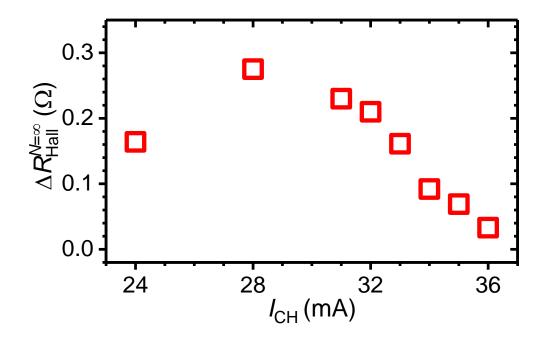

Fitting the curve with an exponential decay allows the calculation of  $\Delta R_{\text{Hall}}$  if the number of read/write cycles is set to  $\infty$ . Figure 5 shows the values of  $\Delta R_{\text{Hall}}$  at  $N = \infty$  for different

levels of channel current, indicating the highest  $\Delta R_{\text{Hall}}$  at 28 mA after infinite iterations. As noted in a previous paper,  $\alpha$ , or the total system variation can be determined by  $\alpha \equiv \frac{\text{dynamic range}}{\text{standard deviation}} \times 100$  (previously 43%). Measuring a new set of 36 SOT devices at the maximum write current of 28 mA shows a dynamic range of 0.23  $\Omega$  with a standard deviation of 0.0048  $\Omega$ , leading to an  $\alpha$  of 2.1 %. This percentage fits within the prediction of the simulation of the previous work, which showed that for an ANN with ten 10×10 unique patterns, an  $\alpha$  of 10% or less is necessary.

#### 3.3 Investigation of the reason behind the decay of $\Delta R_{Hall}$ .

To further improve the efficiency of the ANN operation, an investigation into the reason behind the  $\Delta R_{\text{Hall}}$  decay will allow for a wider dynamic range at current levels that do not induce R<sub>Hall</sub> decay. Because the SOT devices do not breakdown completely after applying high magnitudes of current, there is possibly an important aspect of analogue-like SOT switching that is weakening. As stated in the introduction, the SOT switching is due in part to two major factors: SOT, which arises from the spin-orbit interaction inside the AFM layer or AFM/FM interface when a charge current is applied, and the exchange bias field, arising from the exchange coupling at the interface of the AFM and FM layers. Furthermore, the analogue-like switching is mainly due to the unique crystalline structure of the AFM<sup>29</sup>. Because so many elements that lead to the operation of the device arise from the AFM layer, we expect that the cause of the decay is a current-induced effect on the AFM structure. Although an extensive investigation of the effects of SOT or the changes in the crystalline structure is required, a rather simple experiment can show whether high current magnitudes applied for several cycles affects the exchange bias field strength. To do so, an experiment similar to that in Ref. 15 was conducted, where  $R_{\text{Hall}}$ - $I_{\text{CH}}$  measurements of the device were carried out while applying an external magnetic field of different magnitudes in the  $\pm X$ direction.

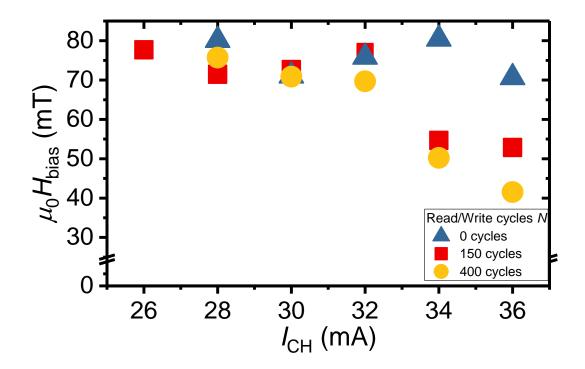

Plotting the resulting exchange bias field  $H_{\text{bias}}$  values as a function of  $I_{\text{CH}}$  shows that after applying 150 read/write cycles, the devices to which an  $I_{\text{CH}}$  of more than 32 mA applied showed a decrease in the effective  $H_{\text{bias}}$  (Fig. 6). It can thus be concluded that high magnitudes of current affect the effective  $H_{\text{bias}}$ . Furthermore, because there is a negligible difference between  $H_{\text{bias}}$  after 150 read/write cycles and after 400 read/write cycles, it can be concluded that the decay of the devices is less dependent on the length of operation than the magnitude of operation current. Therefore, exploring material systems that improve the issues listed above and/or operating such systems considering the decay of device properties caused by too high currents are expected to lead to ANNs with high reliabilities.

# 4. Conclusions

We have explained in detail the procedure of the previously reported work that demonstrated the capabilities of an ANN with 36 SOT devices to execute an associative memory operation. The devices showed the distribution of their  $R_{\text{Hall}}$  values mapped to synaptic weights after applying a learning process to memorize three 3×3 block patterns. However, owing to a high level of the total system variation  $\alpha$ , the direction cosine of the system does not recover to its ideal value. After applying several hundred read/write cycles and measuring the resulting  $\Delta R_{\text{Hall}}$ , we find that high magnitudes of current decay the efficiency of the device. Because the learning process does not rewrite all devices during each iteration of the learning process, some devices decay more than others, leading to the large system variation. We then determine that operating the devices at a safe current of 28 mA can produce negligible amounts of decay, effectively reducing  $\alpha$  to 2.3%, which is small enough for reliable associative memory operation.

While these results are promising for improving the current demonstration, to be able to compete with other hardware-based ANN paradigms and CMOS technology, one aspect to focus on is the read-out mechanism. Using a magnetic tunnel junction showing tunneling magnetoresistance for the read-out operation allows for a higher level of resistance change, and thus a higher level of system-level integration. Furthermore, if the device is patterned into a three-terminal structure, the read and write current paths can be separated, providing design flexibility. These new developments will be achieved through an in-depth study of the material stack structure, device design and device physics, and system-level integration. These new developments will open a discussion on progressing spintronics technology towards a wide range of machine learning paradigms for non-von Neumann architecture applications.

# Acknowledgments

The authors would like to thank H. Akima, S. Sato, Y. Horio, S. Moriya, S. Kurihara, C. Igarashi, T. Hirata, H. Iwanuma, Y. Kawato, and K. Goto for discussion and technical support. This work was supported in part by the R&D Project for ICT Key Technology to Realize Future Society of MEXT, JST-OPERA, JSPS KAKENHI Grant Number 17H06093, JSPS Core-to-Core Program, and Cooperative Research Projects of RIEC (H28/B01, H28/A16, H29/B15).

Template for JJAP Regular Papers (Feb. 2017)

# References

- D. Silver, A. Huang, C. J. Maddison, A. Guez, L. Sifre, G. Van Den Driessche, J. Schrittwieser, I. Antonoglou, V. Panneershelvam, M. Lanctot, S. Dieleman, D. Grewe, J. Nham, N. Kalchbrennerm, I. Sutskever, T. Lillicrap, M. Leach, K. Kavukcuoglu, T. Graepel, and D. Hassabis, Nature 529, 484 (2016).

- P. A. Merolla, J. V. Arthur, R. Alvarez-Icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar, and D. S. Modha, Science 345, 668 (2014).

- B. V. Benjamin, P. Gao, E. McQuinn, S. Choudhary, A. R. Chandrasekaran, J.-M. Bussat, R. Alvarez-Icaza, J. V. Arthur, P. Merolla, and K. Boahen, Proc. IEEE 102, 5 (2014).

- 4. S. B. Furber, F. Galluppi, S. Temple, and L. A. Plana, Proc. IEEE 102, 5 (2014).

- 5. D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, Nature 453, 80 (2008).

- S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, Nano Lett. 10, 1297-1301 (2010).

- D. Kuzum, R. G. D. Jeyasingh, B. Lee, and H. S. P. Wong, Nano Letters 12, 2179-2186 (2012).

- Y. Nishitani, Y. Kaneko, M. Ueda, T. Morie, and E. Fujii, J. Appl. Phys. 111, 124108 (2012).

- G. W. Burr, R. M. Shelby, S. Sidler, C. D. Nolfo, J. Jang, I. Boybat, R. S. Shenoy, P. Narayanan, K. Virwani, E. U. Giacometti, B. N. Kurdi, and H. Hwang, IEEE Transactions on Electron Devices 62, 3498-3507 (2015).

- 10. M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev, and D. B. Strukov, Nature **521**, 61-64 (2015).

- S. Boyn, J. Grollier, G. Lecerf, B. Xu, N. Locatelli, S. Fusil, S. Girod, C. Carrétéro, K. Garcia, S. Xavier, J. Tomas, L. Bellaiche, M. Bibes, A. Barthélémy, S. Saïghi, and V. Garcia, Nature Commun. 8, 14736 (2017).

- 12. N. Locatelli, V. Cros, and J. Grollier, Nat. Mater. 13, 11 (2014).

- 13. A. Sengupta, Z. A. Azim, X. Fong, and K. Roy, App. Phys. Lett. 106, 093704 (2015).

- S. Lequeux, J. Sampaio, V. Cros, K. Yakushiji, A. Fukushima, R. Matsumoto, H. Kubota, S. Yuasa, and J. Grollier, Sci. Rep. 6, 31510 (2016).

- 15. J. Grollier, D. Querlioz, and M. D. Stiles, Proc. IEEE 104, 2024 (2016).

- J. Torrejon, M. Riou, F. A. Araujo, S. Tsunegi, G. Khalsa, D. Querlioz, P. Bortolotti, V. Cros, K. Yakushiji, A. Fukushima, H. Kubota, S. Yuasa, M. D. Stiles, and J. Grollier,

Nature 547, 428 (2017).

- 17. A. Sengupta and K. Roy, App. Phys. Rev. 4, 041105 (2017).

- 18. A. Sengupta and K. Roy, Appl. Phys. Express 11, 11 (2018).

- W. A. Borders, H. Akima, S. Fukami, S. Moriya, S. Kurihara, Y. Horio, and H. Ohno, Appl. Phys. Express 10, 013007 (2017).

- 20. S. Fukami, C. Zhang, S. DuttaGupta, A. Kurenkov, and H. Ohno, Nat. Mater. 15, 535 (2016).

- 21. S. Fukami and H. Ohno, Jpn. J. Appl. Phys. 56, 0802A1 (2017).

- 22. W. H. Meiklejohn and C. P. Bean, Phys. Rev. 102, 1413 (1956).

- 23. I. M. Miron, K. Garello, G. Gaudin, P.-J. Zermatten, M. V. Costache, S. Auffret, S. Bandiera, B. Rodmacq, A. Schuhl, and P. Gambardella, Nature **476**, 189 (2011).

- 24. L. Liu, C.-F. Pai, Y. Li, H. W. Tseng, D. C. Ralph, and R. A. Buhrman, Science **336**, 555 (2012).

- 25. S. Fukami, T. Anekawa, C. Zhang, and H. Ohno, Nature Nanotech 11, 621 (2016).

- 26. W. A. Borders, S. Fukami, and H. Ohno, IEEE Trans. Magn. 53, 6000804 (2017).

- 27. J. J. Hopfield, Proc. Natl. Acad. Sci. U.S.A. 79, 2554 (1982).

- 28. D. H. Ackley and G. E. Hinton, Cogn. Sci. 9, 147 (1985).

- 29. Kurenkov, C. Zhang, S. DuttaGupta, S. Fukami, and H. Ohno, Appl. Phys. Lett. 110, 092410 (2017).

### **Figure Captions**

**Fig. 1.** (Color online) (a) Schematic of the fabricated Hall bar device. Current is swept in the positive X-direction while the anomalous Hall voltage is read across the Y-direction. (b) Experimental data of the anomalous Hall resistance  $R_{\text{Hall}}$  vs channel current  $I_{\text{CH}}$  swept to increasing maximum current ( $I_{\text{MAX}}$ ).

**Fig. 2.** (Color online) Construction of state vectors and representative synaptic weight matrix. (a) Construction of the 3 state vectors for patterns "I", "C", and "T", and (b) the 3 state vectors that represent them. (c) Resulting representative synaptic weight matrix of the 3-pattern system using Eq. (2). The identity matrix multiplied by the number of patterns is subtracted in Eq. 2 because there is no synapse connecting a neuron to itself in this representation.

Fig. 3. (Color online) Illustration of the variation of linear region and dynamic range between devices. The red line represents the linear region and the  $\Delta R_{\text{Hall}}$  area represents the region of  $R_{\text{Hall}}$  values used for synaptic weights -3, -1, 1, and 3.

Fig. 4. (Color online) Measurement setup for resistance decay and results. (a) Measurement setup to measure the change in  $R_{\text{Hall}}$ . To switch the magnetization of the FM layer, 0.3 s duration current pulses with the same magnitude but with different signs are applied. Between each switching pulse, a 0.1 s duration measurement current pulse ( $I_{\text{Meas}}$ ) of 1 mA is applied to measure  $R_{\text{Hall}}$ . (b)  $\Delta R_{\text{Hall}}$  vs number of repetitions of read/write cycles N when  $I_{\text{CH}}$  = 36 mA (red), 34 mA (yellow), and 31 mA (green).

Fig. 5. (Color online) Final  $\Delta R_{\text{Hall}}$  obtained from extending exponential decay fit to  $N = \infty$ .

Fig. 6. (Color online) Experimental values of the exchange bias field after applying  $I_{CH}$  magnitudes in the range of 26 to 36 mA for 0, 150, and 400 cycles.

Fig. 1. (Color Online)

| (c) |     |    |    |    |    |    |    |    |    |

|-----|-----|----|----|----|----|----|----|----|----|

|     | _ 1 | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9_ |

| 1   | 0   | 1  | 3  | 1  | -1 | -1 | 1  | 1  | 1  |

| 2   | 1   | 0  | 1  | 1  | 1  | 3  | -1 | -3 | -1 |

| 3   | 3   | 1  | 0  | 1  | -1 | -1 | 1  | 1  | 1  |

| 4   | 1   | 1  | 1  | 0  | -3 | 1  | -3 | -1 | 3  |

| 5   | -1  | 1  | -1 | -1 | 0  | -1 | -3 | 1  | -3 |

| 6   | -1  | 3  | -1 | 1  | -1 | 0  | 1  | -3 | 1  |

| 7   | 1   | -1 | 1  | -3 | -3 | 1  | 0  | -1 | 3  |

| 8   | 1   | -3 | 1  | -1 | 1  | -3 | -1 | 0  | -1 |

| 9   | 1   | -1 | 1  | 3  | -3 | 1  | 3  | -1 | 0  |

|     |     |    |    |    |    |    |    |    |    |

Fig. 2. (Color)

Color print

Fig. 3. (Color)

Fig. 4. (Color)

Fig. 5. (Color)

Fig. 6. (Color)