## TOHOKU UNIVERSITY

## **Graduate School of Information Sciences**

# **Automatic Performance Tuning Methods for Heterogeneous Computing Systems**

(複合型計算システムにおける性能自動チューニング手法に関する研究)

A dissertation submitted for the degree of Doctor of Philosophy (Information Sciences)

Department of Computer and Mathematical Sciences

by

**Katsuto SATO**

January 16, 2012

#### Automatic Performance Tuning Methods for Heterogeneous Computing Systems

#### Katsuto Sato

#### Abstract

Conventional computing systems, called *homogeneous computing systems*, consist of general purpose processors (CPUs) with the same hardware architecture. Currently, the size of a homogeneous computing system is often limited by the power budget available for the system. Since drastic improvement of power efficiencies is practically hard for CPUs, it is difficult for such a system to significantly increase the system size under assumption of the same power budget. Therefore, the power budget restricts the performance improvement, and it becomes a big program.

Heterogeneous computing systems consist of some different processors that have different architectures, such as general purpose processors (CPUs) and accelerators. A heterogeneous computing system is considered a promising system architecture to achieve high-performance and energy-efficient computing. As accelerators have high floating operation rates and high memory bandwidths, heterogeneous computing systems can achieve high power efficiency. Therefore, heterogeneous computing systems are widely utilized in recent large-scale high performance computing systems. TSUB-AME 2.0 [1] and Roadrunner [2] are well-known as examples of large-scale heterogeneous computing systems. As these systems have many accelerators, a programmer can use multiple accelerators to improve a performance of a program. In these systems, appropriate task assignment is important to efficiently use accelerators of the systems: processor selection and load balancing.

As the sustained performance on an accelerator depends on computations of tasks, programmers need to assign only suitable tasks to accelerators. Assigning an unsuitable task causes serious performance degradation. Moreover, appropriate task assignment is determined at runtime because it often depends on input data and available accelerators. Hence, runtime processor selection is important to exploit the high computing potential of heterogeneous computing systems.

Load-balancing among multiple accelerators is required to efficiently use a heterogeneous computing system that has many accelerators. Basically, programmers must assign tasks to a processor with careful consideration of suitability between a task and a processor. However, since appropriate task assignment completely depends on the configuration of accelerators in a heterogeneous computing system, it is difficult to assign tasks into accelerators in advance. Inappropriate task assignment may cause serious performance degradation in the system.

A Graphics Processing Unit (GPU) is one of accelerators that have high floating-point operation rates and high memory bandwidths. As a standard PC with a GPU can be seen as a widely-available heterogeneous computing system, standard programmers can use a GPU for computation, which is called *GPU computing*. For GPU computing, programmers can write a *kernel* function to define *a task* that is executed on GPUs by using programming frameworks such as CUDA [3] or OpenCL [4].

As accelerators such as GPUs have architecture-specific features useful to improve performance, architecture-specific performance tunings and optimizations such as execution parameter setting and efficient memory accesses are necessary to achieve high performance. However, these tunings and optimizations are difficult and labor-intensive even for expert programmers. Thus, the automatic tunings and optimizations are required to improve sustained performance of accelerators.

To alleviate these difficulties, programming frameworks or system software should be equipped with the functionality of the performance tunings. To this end, automation of performance tunings

is strongly required. In this dissertation, automatic performance tuning methods including runtime processor selection, program optimization, and load balancing among accelerators are proposed to overcome the above difficulties.

In Chapter 2, the SPRAT framework consisting of a domain-specific programming language and its runtime environment is proposed to automatically select the appropriate processor at runtime. The SPRAT compiler translates a program written in the SPRAT language to a code written in C++ for a CPU and a code written in CUDA for GPUs, respectively. The SPRAT runtime environment automatically selects an appropriate processor for each task based on the performance prediction. In the performance prediction of SPRAT, a linear prediction model is built for each program. In addition, runtime processor selection based on energy efficiency is performed by using the prediction model and the parameters of power consumption. The effects of runtime processor selection for performance-aware and energy-aware computing are evaluated. From the evaluation results, it is demonstrated that the SPRAT framework enables even a non-expert programmer to benefit from the use of GPUs without risks of performance degradation.

In Chapter 3, to improve the sustained performance, two performance tuning strategies are proposed; some optimization methods to improve sustained memory bandwidth and a tuning method of execution parameters. In GPU computing, improving sustained memory bandwidth is important to achieve high performance. Hence, Chapter 3 first proposes one tuning strategy including two optimization methods of memory accesses. *Reusable data prefetching* finds highly-reusable data blocks and places those blocks on an on-chip memory to shorten the memory access latency. *Adjusting access patterns* removes the inefficient memory access patterns in the program by using an on-chip memory as a read buffer. Furthermore, Chapter 3 proposes the other tuning strategy to automatically find the optimal configuration of execution parameters based on profiling data. The proposed tuning method runs a program with several configurations and measures its sustained performances for profiling. Evaluation results indicate that the two performance tuning strategies are effective to improve sustained performance of CUDA programs.

In Chapter 4, an online task scheduling method is proposed to realize automatic load balancing among multiple accelerators. Automatic load balancing by online task scheduling is effective to extract the potential of multiple accelerators. For the task scheduling, accurate performance prediction and dependency analysis are necessary. Hence, Chapter 4 first proposes a performance prediction method and a dependency analysis method. Then, an online scheduling method is proposed. The proposed performance prediction method uses not only past execution times but also the argument values passed to the tasks. In the dependency analysis, unnecessary data dependencies and synchronization points are removed to make many more parallel tasks. The online task scheduling method is performed based on the *minimum completion time* (MCT) algorithm. In this method, a task in a program is assigned to an appropriate accelerator that can early complete the task. Evaluation results show that the proposed prediction method achieves higher accuracy than conventional methods. The online task scheduling method can automatically and finely balance the loads between different accelerators, and efficiently use their performances.

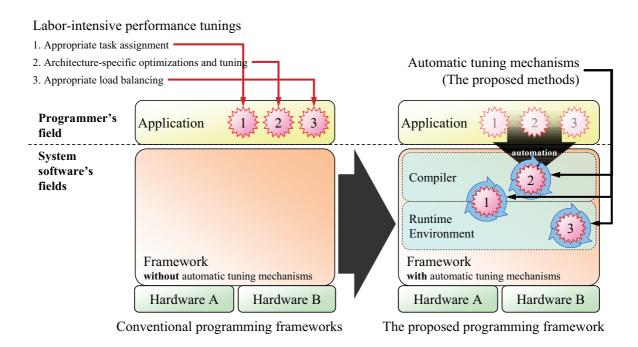

In conclusion, this dissertation establishes three approaches that enable programmers to fully exploit the computing potential of heterogeneous computing systems. The proposed methods can automate performance tuning and optimizations, and realize a programming framework with automatic performance tuning mechanisms. This programing framework enables programmers to describe programs without labor-intensive performance tunings and risks of performance degradation.

# Acknowledgments

I have obtained a lot of supports and warm leading from many people of Tohoku University. I would like to gratefully acknowledge all of them.

First of all, I would like to express sincere gratitude to my research supervisor, Associate Professor Hiroyuki Takizawa who has conducted me to this research field and has given abundant leading. I would also like to express cordial acknowledgment to Professor Hiroaki Kobayashi who has supported and offered invaluable assistance. They have given me great help and have encouraged me in my research activity. I would like to thank Professor Kazuhiro Nakahashi and Professor Takafumi Aoki for their thoughtful review of my dissertation and valuable comments. I wish to express my appreciation to Assistant Professor Ryusuke Egawa for invaluable discussion and his considerable advices.

I would like to thank Associate Professor Hideaki Goto for his support and helpful comments. I wish to express special thanks to Dr. Kazuhiko Komatsu and Dr. Yoshitomo Murata who give me important assistance and invaluable suggestions in my research. I would also like to express my appreciation to my irreplaceable colleagues; Mr. Yusuke Funaya, Mr. Yoshiei Sato, and Mr. Masayuki Sato. We have encouraged each other and discussed many themes in various research topics. Special thanks go to the member of the heterogeneous computing project team, Mr. Kentaro Koyama, Mr. Yusuke Arai, and Mr. Makoto Sugawara for the meaningful discussions.

Finally, I express the deep acknowledgement to my family. I would like to thank my parents for their affectionate support. I would also like to thank my sister for warm encouragement.

January, 16, 2012 Sato, Katsuto

# **Contents**

| Al             | ostrac | et      |                                                              | i   |

|----------------|--------|---------|--------------------------------------------------------------|-----|

| A              | cknow  | vledgme | ents                                                         | iii |

| 1 Introduction |        |         | n                                                            | 1   |

|                | 1.1    | Backg   | round                                                        | 1   |

|                | 1.2    | Graph   | ics Processing Units as Accelerators                         | 6   |

|                | 1.3    | Object  | ive of the Dissertation                                      | 8   |

|                | 1.4    | Organi  | ization of the Dissertation                                  | 10  |

| 2              | A D    | omain-s | specific Language with Runtime Processor Selection           | 11  |

|                | 2.1    | Introdu | uction                                                       | 11  |

|                | 2.2    | Relate  | d Work                                                       | 14  |

|                |        | 2.2.1   | Programming Environments for Heterogeneous Computing Systems | 14  |

|                |        | 2.2.2   | Performance Model and Prediction                             | 16  |

|                | 2.3    | A Don   | nain-specific Language with Runtime Processor Selection      | 19  |

|                |        | 2.3.1   | Overview                                                     | 19  |

|                |        | 2.3.2   | Stream Programming language with Runtime Auto-Tuning (SPRAT) | 19  |

|                |        | 2.3.3   | Performance Prediction and Processor Selection               | 23  |

|                | 2.4    | Evalua  | ntion                                                        | 29  |

|                |        | 2.4.1   | Experimental Setup                                           | 29  |

|                |        | 2.4.2   | Evaluation of Performance-aware Processor Selection          | 29  |

|                |        | 2.4.3   | Evaluation of Energy-aware Processor Selection               | 31  |

|                | 2.5    | Concli  | iding Remarks                                                | 37  |

| 3   | Auto  | omatic 1 | Performance Tuning for the Domain-specific Language                   | <b>4</b> 1 |

|-----|-------|----------|-----------------------------------------------------------------------|------------|

|     | 3.1   | Introd   | uction                                                                | 41         |

|     | 3.2   | Relate   | d Work                                                                | 43         |

|     |       | 3.2.1    | Performance Tuning in CUDA                                            | 43         |

|     |       | 3.2.2    | Optimization Tools for GPU computing                                  | 46         |

|     | 3.3   | Optim    | izing Methods Based on Architectural Features                         | 48         |

|     |       | 3.3.1    | Optimization Methods for Memory Accesses                              | 48         |

|     |       | 3.3.2    | Automatic Performance Tuning of the CTA configuration                 | 56         |

|     | 3.4   | Evalua   | ation                                                                 | 63         |

|     |       | 3.4.1    | Benchmarks for Evaluations                                            | 63         |

|     |       | 3.4.2    | Evaluation of Optimization Methods for Memory Accesses                | 63         |

|     |       | 3.4.3    | Evaluation of the CTA Configuration Tuning                            | 68         |

|     | 3.5   | Conclu   | uding Remarks                                                         | 77         |

| 4   | Onli  | ine Tasl | k Scheduling in Standard Programming Environments                     | 79         |

|     | 4.1   | Introd   | uction                                                                | 79         |

|     | 4.2   | Relate   | d Work                                                                | 82         |

|     |       | 4.2.1    | OpenCL                                                                | 82         |

|     |       | 4.2.2    | Performance Prediction Methods                                        | 84         |

|     |       | 4.2.3    | Methods for Dependency Analysis                                       | 86         |

|     |       | 4.2.4    | Methods for Task Scheduling                                           | 87         |

|     | 4.3   | Online   | e Task Scheduling Based on Performance Predictions                    | 90         |

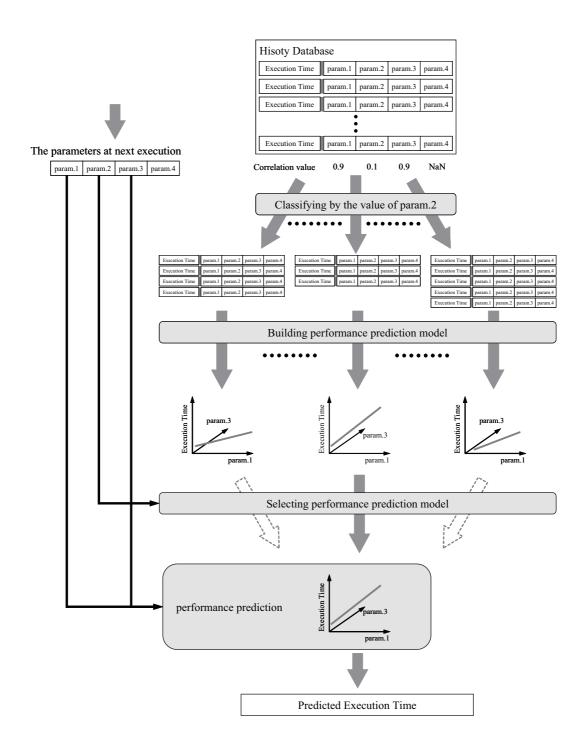

|     |       | 4.3.1    | History-based Performance Prediction with Profile Data Classification | n 90       |

|     |       | 4.3.2    | Data and Event Dependency Analysis Methods                            | 95         |

|     |       | 4.3.3    | Online Task Scheduling Based on the MCT Algorithm                     | 100        |

|     | 4.4   | Evalua   | ations                                                                | 103        |

|     |       | 4.4.1    | Evaluation of the Performance Prediction                              | 103        |

|     |       | 4.4.2    | Evaluation of the Performance Improvement by Online Task Schedul-     |            |

|     |       |          | ing                                                                   | 109        |

|     | 4.5   | Conclu   | uding Remarks                                                         | 117        |

| 5   | Con   | clusion  | s                                                                     | 119        |

| Ril | hling | ranhv    |                                                                       | 123        |

# **List of Tables**

| 2.1 | Specifications of GPUs used for evaluation                                 | 29  |

|-----|----------------------------------------------------------------------------|-----|

| 2.2 | Power consumption of each system configuration                             | 31  |

| 3.1 | The memory hierarchy in CUDA                                               | 44  |

| 3.2 | The bandwidths ratios between coalesced and uncoalesced memory accesses    |     |

|     | for several GPUs                                                           | 55  |

| 3.3 | Experimental setup in Section 3.4.2                                        | 65  |

| 3.4 | Experimental setup in Section 3.4.3                                        | 69  |

| 4.1 | The types of data dependencies among tasks                                 | 95  |

| 4.2 | Experimental setup to evaluate the proposed prediction method              | 103 |

| 4.3 | Experimental setup to evaluate the proposed online task scheduling method. | 109 |

# **List of Figures**

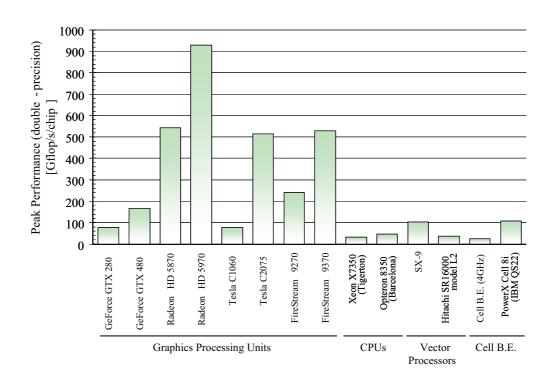

| 1.1 | Peak double-precision floating-point operation rates of several processors | 2  |

|-----|----------------------------------------------------------------------------|----|

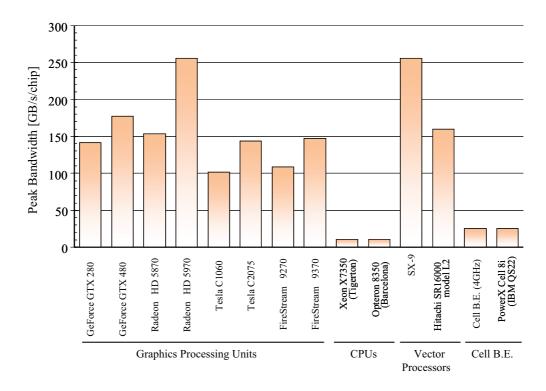

| 1.2 | Peak memory bandwidths of several processors                               | 2  |

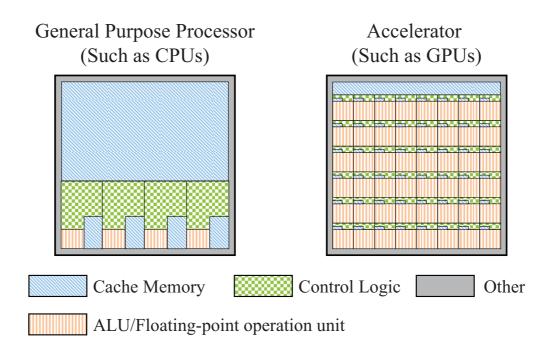

| 1.3 | The difference in usage of hardware resources for CPUs and accelerators    | 3  |

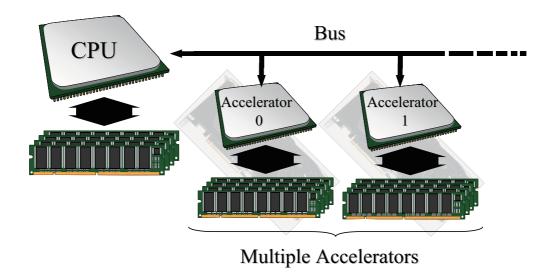

| 1.4 | An example of heterogeneous computing systems                              | 4  |

| 1.5 | Performance tunings in programming frameworks                              | 9  |

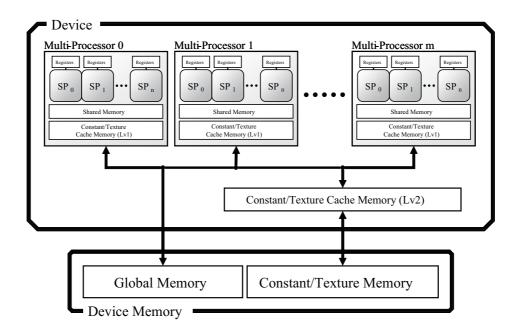

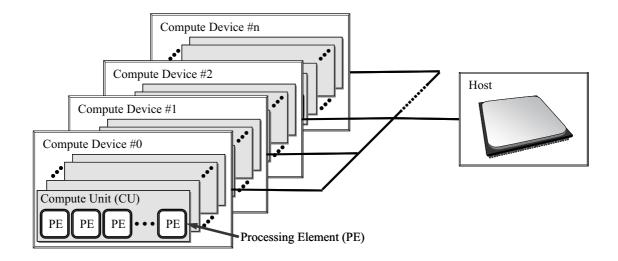

| 2.1 | The hardware architecture assumed in CUDA                                  | 15 |

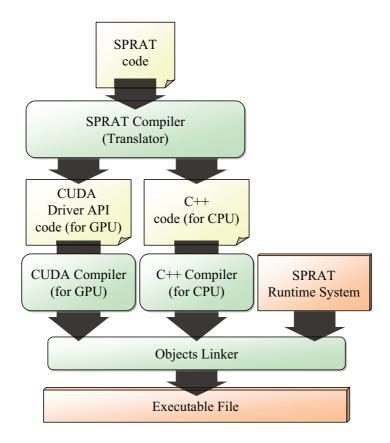

| 2.2 | The compiling flow of a SPRAT program                                      | 20 |

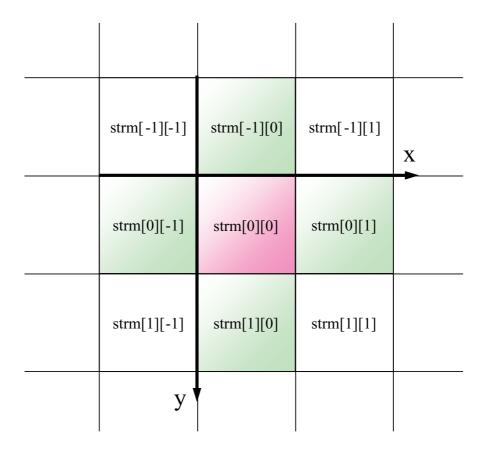

| 2.3 | The coordinate in gather access                                            | 22 |

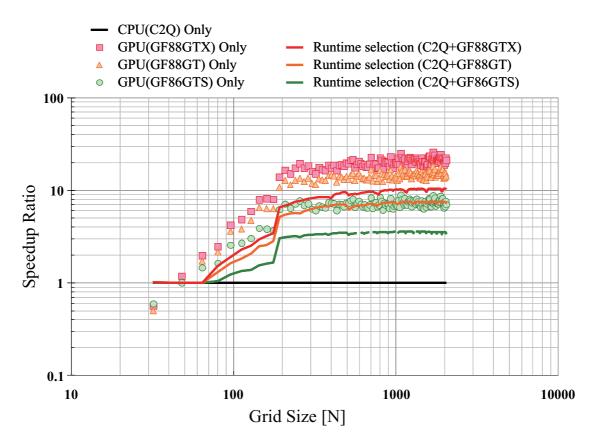

| 2.4 | Speedup ratio of the CFD simulation                                        | 30 |

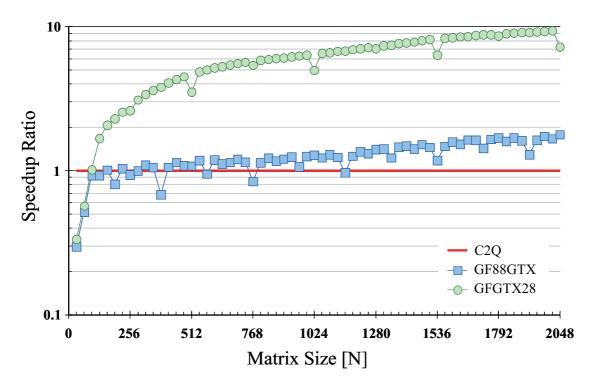

| 2.5 | Speedup ratio of the LU decomposition                                      | 33 |

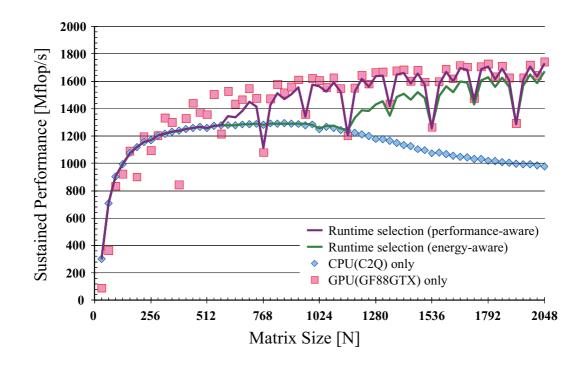

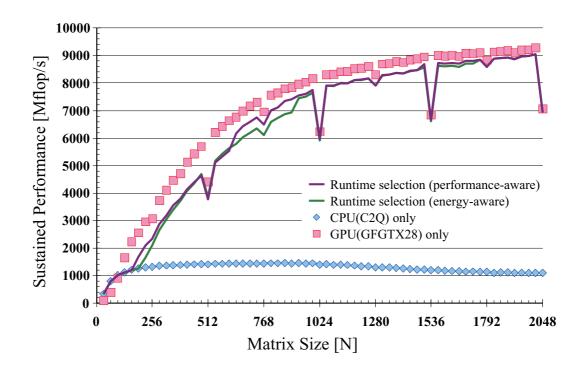

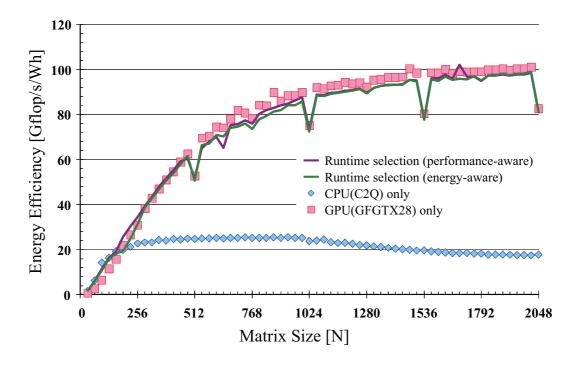

| 2.6 | Sustained performance of C2Q and GF88GTX                                   | 35 |

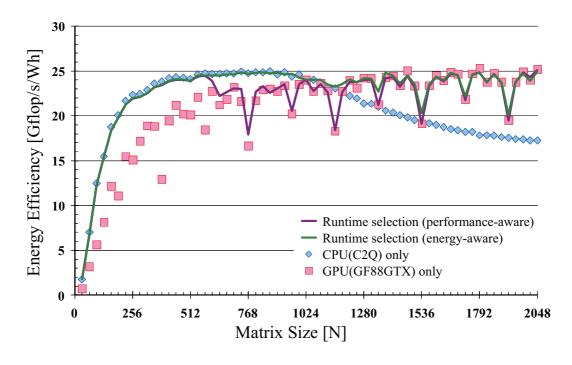

| 2.7 | Energy efficiency of C2Q and GF88GTX                                       | 35 |

| 2.8 | Sustained performance of C2Q and GFGTX28                                   | 36 |

| 2.9 | Energy efficiency of C2Q and GFGTX28                                       | 36 |

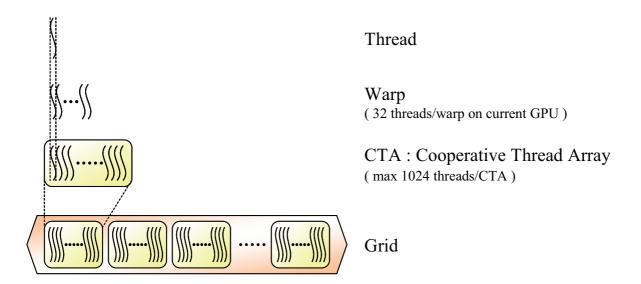

| 3.1 | The thread hierarchy in CUDA                                               | 43 |

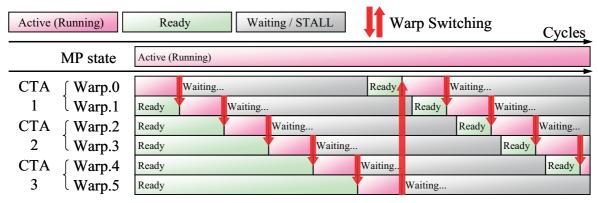

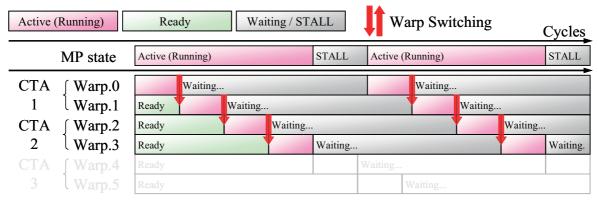

| 3.2 | Warp switching execution in CUDA                                           | 45 |

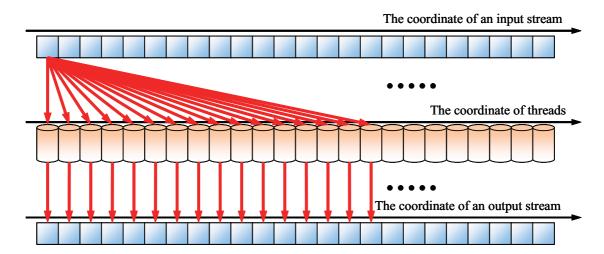

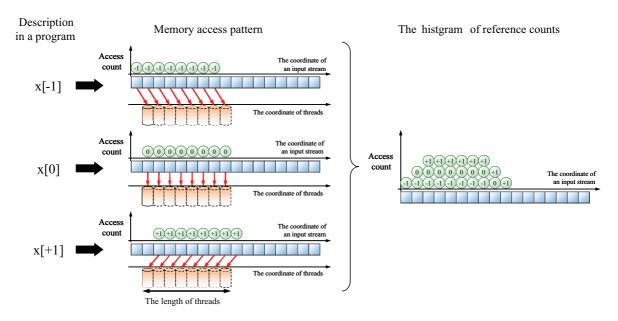

| 3.3 | The memory access pattern of a gather stream by an absolute index          | 49 |

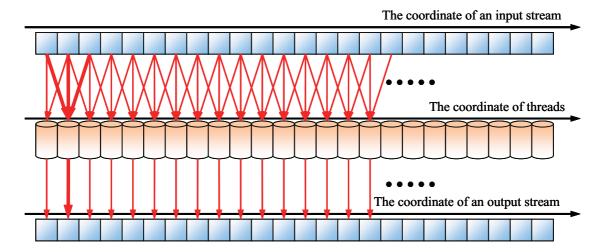

| 3.4 | The memory access pattern of a gather stream by a relative index           | 49 |

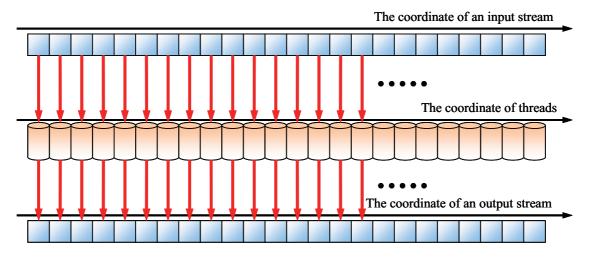

| 3.5 | The memory access pattern of in and out streams                            | 49 |

| 3.6 | Estimation for the histogram of memory access counts                       | 51 |

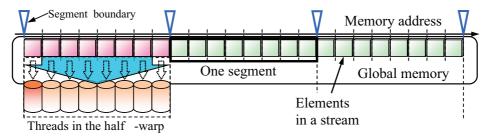

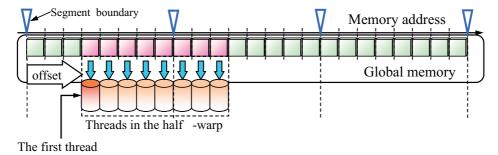

| 3.7 | Examples of a global memory access in CUDA                                 | 52 |

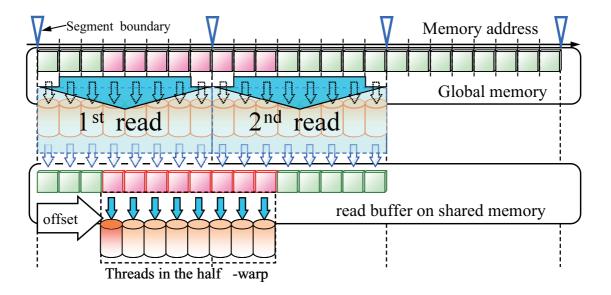

| 3.8 | The overview of the proposed method to adjust the access pattern           | 53 |

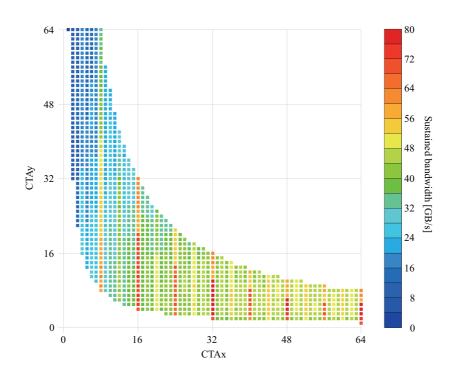

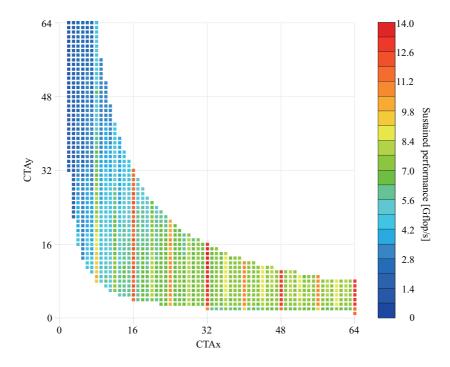

| 3.9 | Relationship between sustained bandwidths and CTA configurations on the    |    |

|     | copy kernel                                                                | 58 |

| 3.10 | Relationship between sustained computing performances and CTA configu-        |     |

|------|-------------------------------------------------------------------------------|-----|

|      | rations on the saxpy kernel                                                   | 58  |

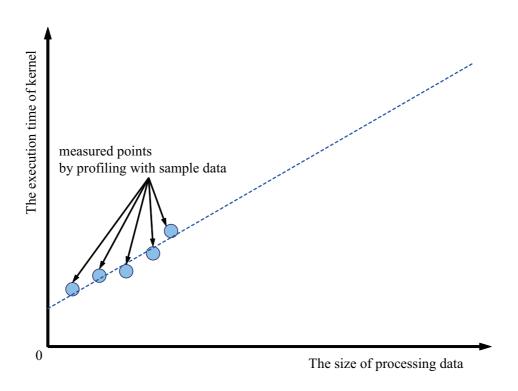

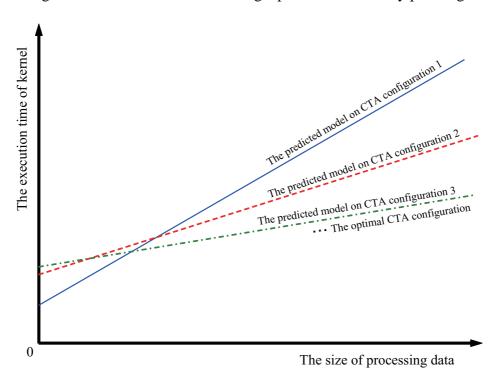

| 3.11 | The method of building a prediction model by profiling                        | 62  |

| 3.12 | The policy of selecting the optimal CTA configuration                         | 62  |

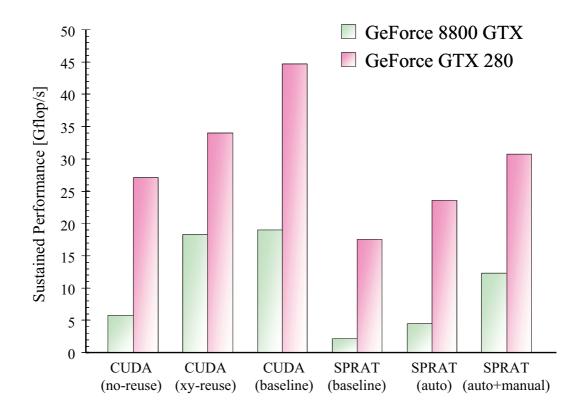

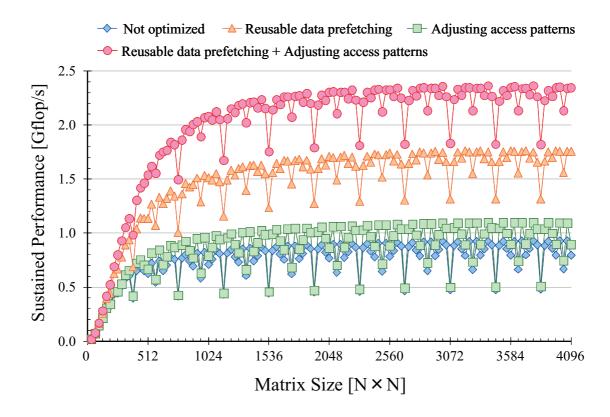

| 3.13 | Evaluation results with the Himeno benchmark                                  | 66  |

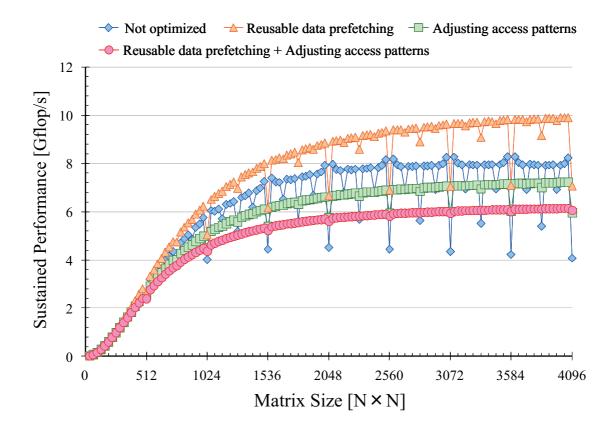

| 3.14 | Evaluation results with the LU decomposition. (GeForce 8800 GTX)              | 67  |

| 3.15 | Evaluation results with the LU decomposition. (GeForce GTX 280)               | 68  |

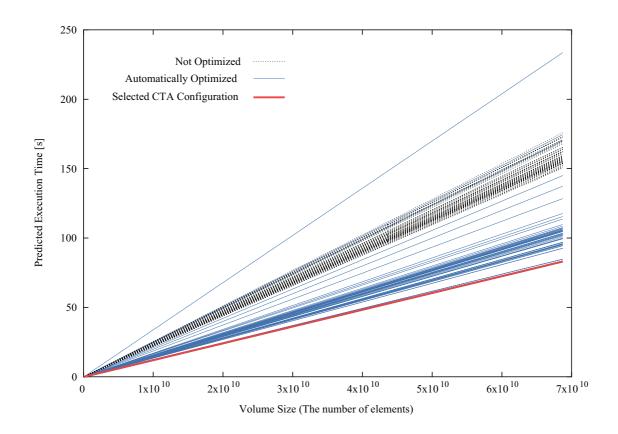

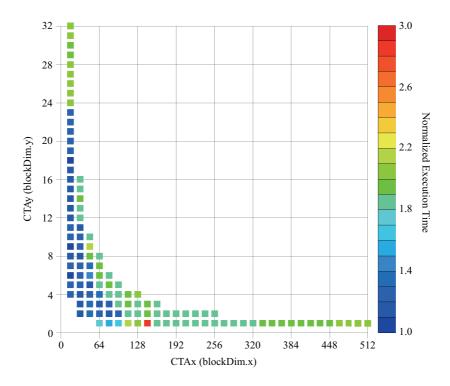

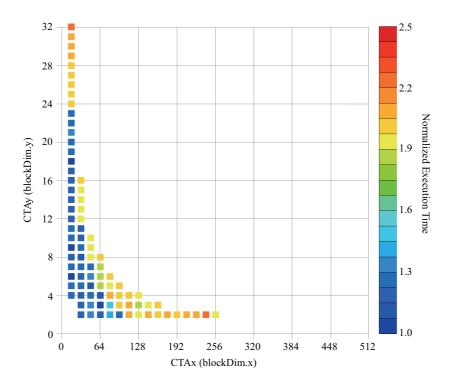

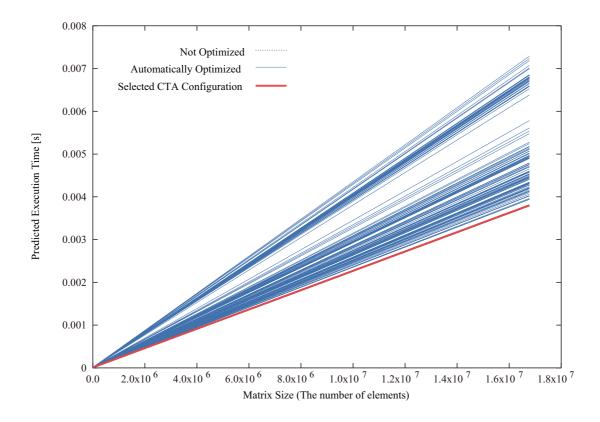

| 3.16 | The performance model of each CTA configuration on the Himeno benchmark.      | 70  |

| 3.17 | The predicted execution time of each CTA configuration on the Himeno          |     |

|      | benchmark                                                                     | 71  |

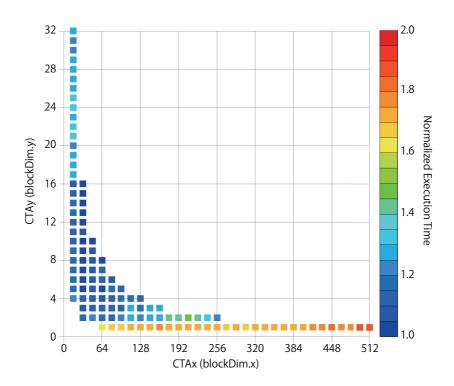

| 3.18 | The actual execution time of each CTA configuration on the Himeno bench-      |     |

|      | mark                                                                          | 71  |

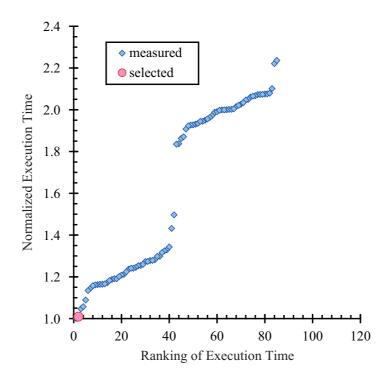

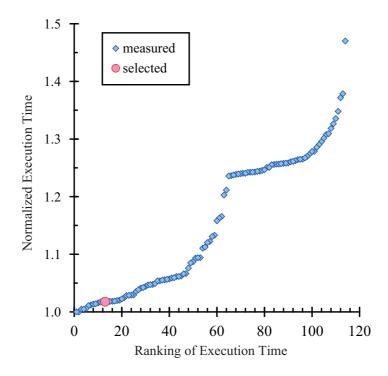

| 3.19 | The ranking of actual execution time on the Himeno benchmark                  | 72  |

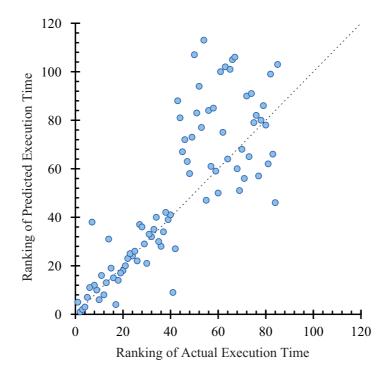

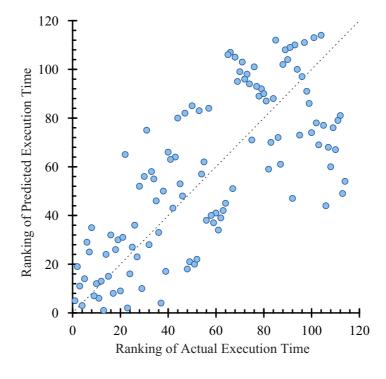

| 3.20 | The correlation between the predicted and the actual rankings of CTA con-     |     |

|      | figurations on the Himeno benchmark                                           | 72  |

| 3.21 | The performance model of each CTA configuration on the LU decomposition.      | 73  |

| 3.22 | The predicted execution time of each CTA configuration on the LU decom-       |     |

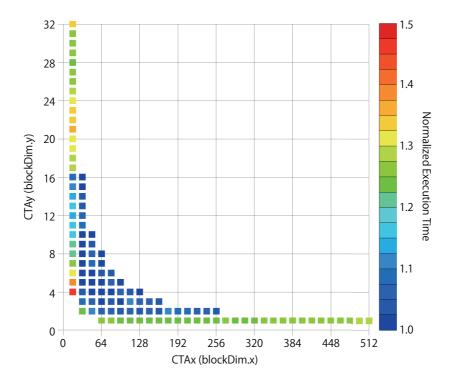

|      | position                                                                      | 74  |

| 3.23 | The actual execution time of each CTA configuration on the LU decomposition.  | 74  |

| 3.24 | The ranking of actual execution time on the LU decomposition                  | 75  |

| 3.25 | The correlation between the predicted and the actual rankings of CTA con-     |     |

|      | figurations on the LU decomposition                                           | 75  |

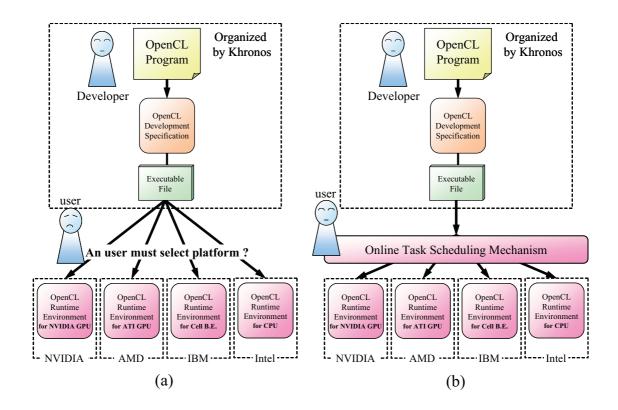

| 4.1  | The problem of (a) appropriate task assignment and (b) the proposed solution. | 80  |

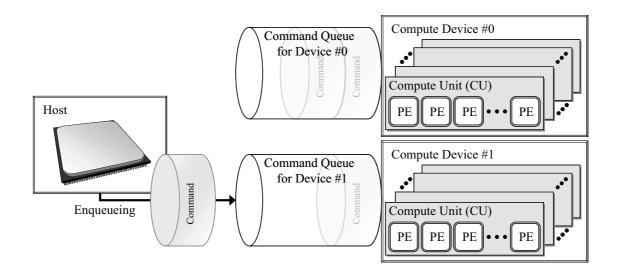

| 4.2  | The platform model of OpenCL                                                  | 82  |

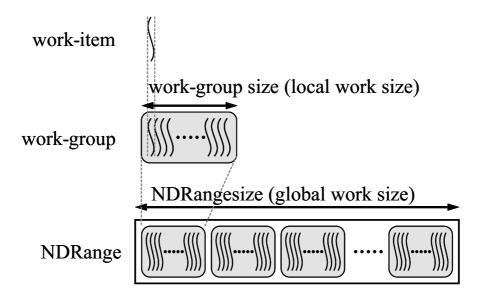

| 4.3  | The thread hierarchy of OpenCL                                                | 83  |

| 4.4  | The queuing model of OpenCL                                                   | 84  |

| 4.5  | Prediction procedure of the proposed method                                   | 91  |

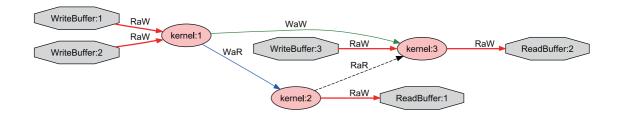

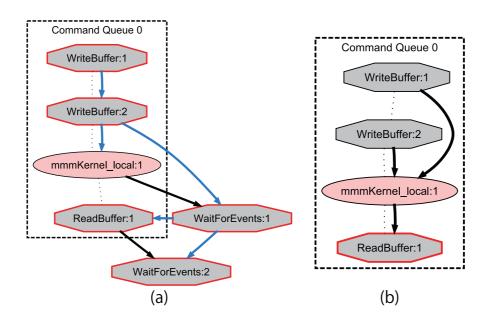

| 4.6  | Examples of data dependencies among tasks                                     | 96  |

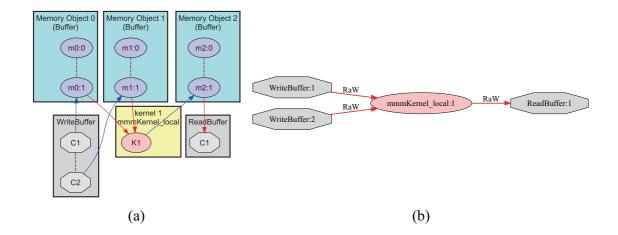

| 4.7  | Examples of (a) a memory access graph and (b) a data dependency graph for     |     |

|      | matrix multiplication                                                         | 97  |

| 4.8  | Examples of event dependency graphs for matrix multiplication. (a) The        |     |

|      | graph of unoptimized program. (b) The graph of optimized program              | 100 |

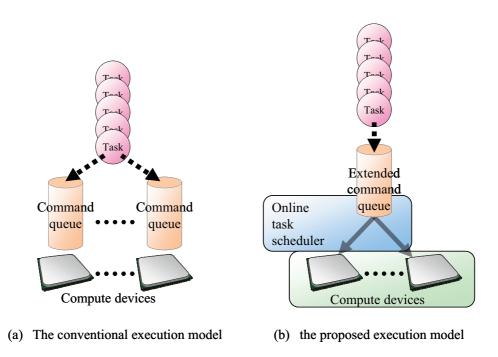

| 4.9  | The conventional and proposed execution models in OpenCL                      | 101 |

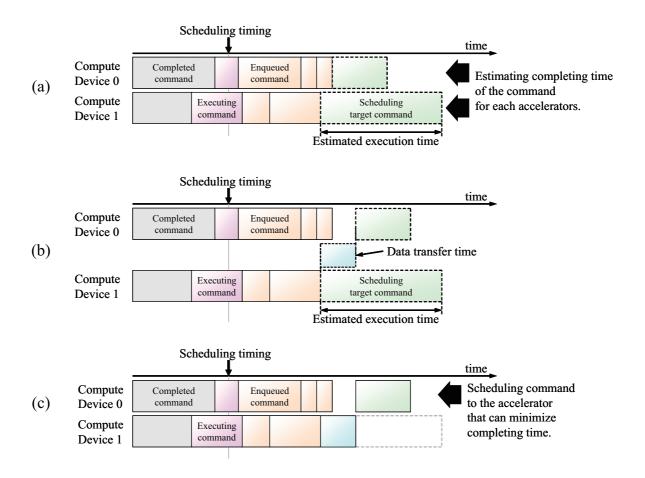

| 4.10 | The procedure of the proposed online scheduling method based on the MCT    |     |

|------|----------------------------------------------------------------------------|-----|

|      | algorithm                                                                  | 102 |

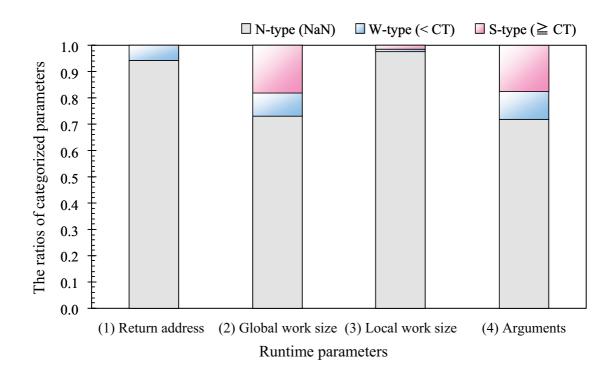

| 4.11 | Usage of runtime parameters                                                | 104 |

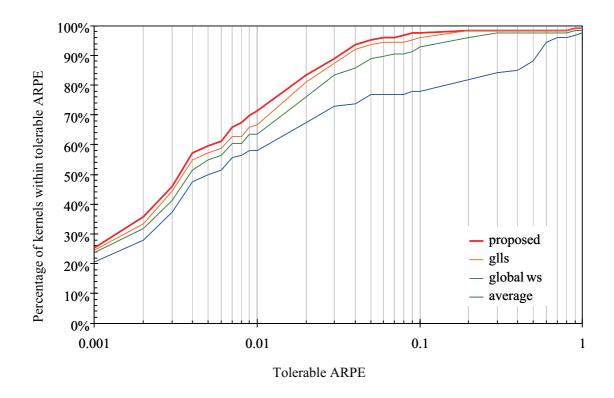

| 4.12 | Percentage of kernels within tolerable ARPE                                | 105 |

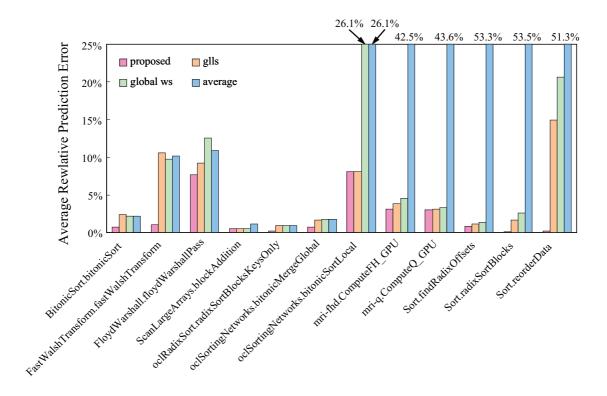

| 4.13 | Comparison results of ARPE in the cases where the proposed method out-     |     |

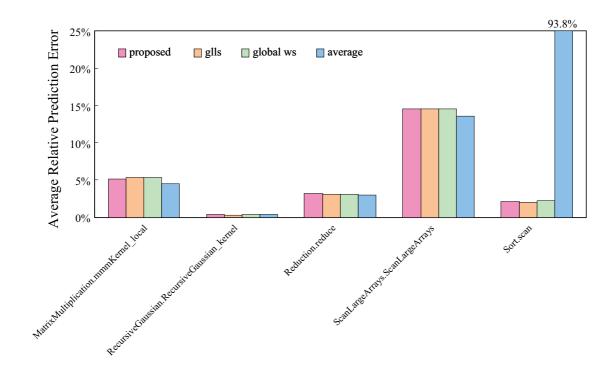

|      | performs the others                                                        | 107 |

| 4.14 | Comparison results of ARPE in the cases where the accuracy of the proposed |     |

|      | method is less than those of the others                                    | 108 |

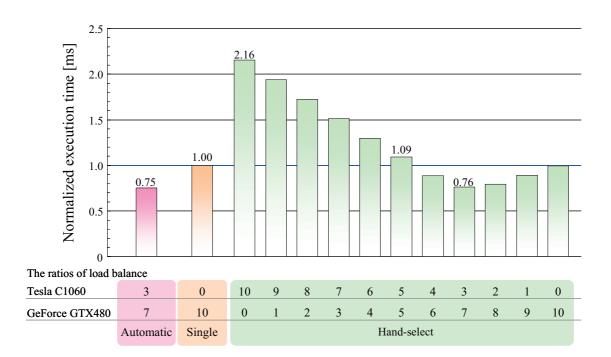

| 4.15 | The evaluation results of the MonteCarloAsian                              | 111 |

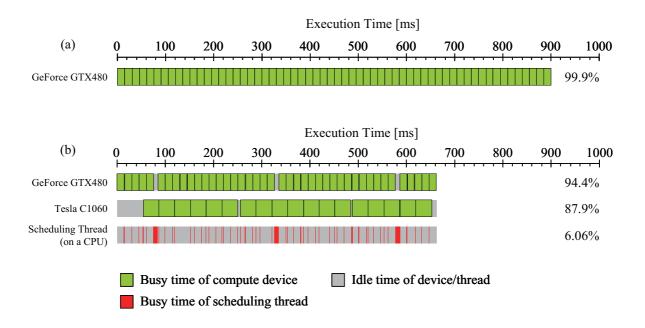

| 4.16 | The operating rates of GPUs and a scheduling thread. (a) the Single imple- |     |

|      | mentation. (b) the <i>Automatic</i> implementation                         | 112 |

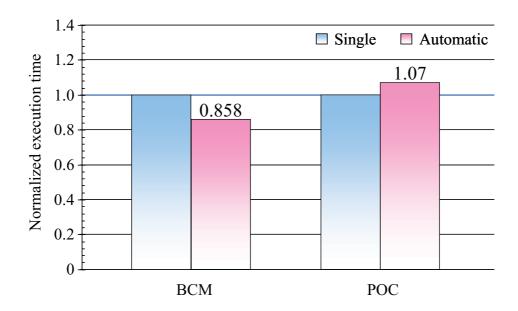

| 4.17 | Evaluation results of the POC and BCM benchmarks                           | 114 |

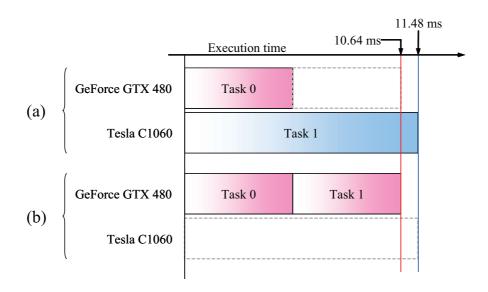

| 4.18 | Task assignment in the POC benchmark. (a) The case of balancing loads.     |     |

|      | (b) The case of using only a GPU                                           | 115 |

# **List of Algorithms**

| 1 | Pseudo code of automatic tuning | ( |

|---|---------------------------------|---|

|   |                                 |   |

# Listings

| 2.1 | A sample code of a reference stream                          | 21 |

|-----|--------------------------------------------------------------|----|

| 2.2 | An equivalent code for the kernel code                       | 21 |

| 2.3 | A sample code of saxpy written in the SPRAT language         | 23 |

| 2.4 | The CFD program written in the SPRAT language                | 38 |

| 2.5 | The LU decomposition written in the SPRAT language           | 40 |

| 3.1 | The sample code using an absolute indexing operator          | 50 |

| 3.2 | The sample code using relative indexing operators            | 50 |

| 3.3 | The code of the saxpy kernel                                 | 57 |

| 3.4 | The main kernel of the Himeno benchmark implemented by SPRAT | 64 |

| 3.5 | The main kernel of the LU decomposition implemented by SPRAT | 64 |

# Chapter 1

# Introduction

## 1.1 Background

A conventional computing system has generally been *homogeneous* and consisted of general-purpose processors, called CPUs, with the same architecture. However, it is difficult for CPUs to drastically improve their power efficiencies. As a result, the size of such a system is limited by the given power budget. Although the most popular way to improve the system performance is to increase the system size, it is difficult to further increase the size of such a system without increasing the power consumption.

Figures 1.1 and 1.2 show the peak performances and the peak memory bandwidths of various processors. In these figures, accelerators such as *Graphics Processing Units(GPUs)* have higher performances and memory bandwidths than typical CPUs. This is because CPUs use a huge amount of hardware resource for large cache memories and complicated control logics to reduce the latency of instruction execution, while GPUs use most hardware resource for computation as shown in Figure 1.3. Although GPUs increase power consumption at a certain level, they usually improve the performance per watt for data-parallel processing due to their high peak performances and memory bandwidths, and thus improve the energy efficiency. Therefore, accelerators have become important components to achieve a higher performance under assumption of a limited power budget.

However, as accelerators are usually assumed to be controlled by CPUs, a computing system needs to have different kinds of processors, CPUs and accelerators. CPUs are used for I/O processing, communications, and complicated program flow controls. On the other hand, accelerators are used for massive data-parallel processing with high power efficiency.

Figure 1.1: Peak double-precision floating-point operation rates of several processors.

Figure 1.2: Peak memory bandwidths of several processors.

Figure 1.3: The difference in usage of hardware resources for CPUs and accelerators.

Hence, *heterogeneous computing systems* consisting of CPUs and accelerators are promising to achieve both high performance and high power efficiency, i.e. *high energy efficiency*.

In heterogeneous computing systems, to achieve both high performance and high power efficiency, each task must be appropriately assigned to one processor in the system. By the appropriate assignment of the tasks, the execution time of a computation is shortened, and hence the energy consumption is reduced; the energy efficiency is improved. However, inappropriate task assignment causes serious performance degradations. Hence, programmers have to appropriately assign tasks to processors with carefully considering the combination of a given computation and an available processor.

Figure 1.4 shows an example of heterogeneous computing systems. A heterogeneous computing system consists of multiple computing nodes, each of which has at least one CPU and one accelerator. Accelerators have their own memory spaces, called *device memories*, which are independent of main memory spaces managed by a CPU. Therefore, explicit data management is required for collaborative work of CPUs and accelerators. As the overhead of data transfer between a CPU and accelerators is not negligible in many cases, one difficulty in task assignment is to ensure that the performance gain is larger than the performance loss due to the overhead. Hence, it is required to consider the data transfer overhead for

Figure 1.4: An example of heterogeneous computing systems.

appropriate task assignment.

If there are multiple accelerators in a heterogeneous computing system, another difficulty is to decide which accelerator executes a task. If an application has many *parallel tasks* that can be independently executed, load balancing among multiple accelerators is needed to minimize the execution time. As programmers do not always know available accelerators and the overhead of data transfers in advance of execution, dynamic load balancing among multiple accelerators is required to exploit their computing power. However, it is difficult and labor-intensive even for expert programmers to balance the loads among accelerators.

To fully exploit the system performance, it is needed to optimize a program according to the architecture of every accelerator in the system. For a conventional processor such as a CPU, a program has mainly been optimized to improve the ratio of cache hits and to parallelize for use of multiple cores. On the other hand, accelerators have execution parameters that affect the sustained performance, and some of the parameters must be specified at execution. As those parameters strongly depend on the accelerator to be used for execution, knowledge and programming experience of the accelerator are required for programmers to optimally determine the parameters. Hence, it is also difficult and labor-intensive to find the optimal parameter setting.

As described above, there are many difficulties to achieve high sustained performance because of complicated and labor-intensive performance tunings. Hence, programming frameworks or system software must deal with some performance tunings to alleviate difficulties of performance tunings. To handle these performance tunings by programming frameworks, it is required to establish automatic performance tuning methods that carry out appropriate task assignment and tuning of execution parameters. Therefore, this dissertation discusses strategies to automate labor-intensive performance tunings.

## 1.2 Graphics Processing Units as Accelerators

Among several accelerators, GPUs draw attention as accessible accelerators that have high floating-point operation rates and high memory bandwidths. A GPU is originally designed to accelerate computation in CG rendering, called a *graphics computation*. Those computations can be offloaded to a GPU so as to alleviate loads on the CPU. The performance of GPUs has been improved to generate higher-quality images. Moreover, their programmability is also extended to support more advanced rendering techniques.

To improve the programmability, a *programmable shader* has been introduced to GPUs. A programmable shader enables a programmer to describe and execute a user-defined tiny program to implement more advanced effects of computer graphics. Programmers can access the programmable shaders via graphics *application programming interfaces* (APIs) and special shader languages such as Cg [5], HLSL [6], and GLSL [7]. With shader programming efforts to trick GPUs, even a non-graphics computation can exploit their computing power. These trials are called *general purpose computation on GPUs* (GPGPU).

In 2007, NVIDIA announced *Compute Unified Device Architecture* (CUDA)[3]. Unlike the previous shader programming methods, CUDA does not require graphics API to use GPUs for computation and is the first programming framework for *GPU computing*. CUDA provides an extended C language, called C for CUDA, and several algorithms can be freely implemented with a few constraints, which is generally so-called *programming flexibility*. Shader programming languages have strong constraints on the programming models, and programmers must describe programs with consideration for these constraints. However, CUDA eliminates most of the constraints and enables a programmer to develop a program in a similar fashion to the conventional C language. So far, there have been many reports to demonstrate that CUDA can accelerate various kinds of non-graphics applications [8]. In CUDA, a computation-intensive part of a program is offloaded to a GPU for acceleration, and the other is executed on a CPU. The offloadable part of a program is called a *CUDA kernel*. As a GPU works well for data-parallel processing, data-parallel processing parts of a program are usually rewritten as CUDA kernels.

Programmers can implement several algorithms for GPUs by using the CUDA language. However, to achieve a high performance, a programmer has to learn not only the CUDA language but also the architectural features of GPUs. The architectures of GPUs are drastically changed according to their generations and grades. It is strongly needed to optimize a program for a particular GPU architecture. Without architecture-aware optimizations,

the sustained performance would be very low. Moreover, as a program written in the CUDA language, called a *CUDA program*, can be directly executed only on NVIDIA's GPUs, it is impossible to switch one kind of processor to another of processor during the execution of a program.

In 2009, Khronos group proposed OpenCL that is a standard programming interface for various accelerators including GPUs [4]. A program written in OpenCL, called an *OpenCL program*, can be executed on different accelerators without any modification of the program. However, performance tunings such as optimizing task assignment and tuning of execution parameters are still required, and the sustained performance significantly depends on the performance tunings.

As mentioned above, CUDA and OpenCL enable programmers to describe a program that can work with GPUs. However, complicated and labor-intensive performance tunings are still required to effectively use GPUs. Especially, if the optimal tuning parameter depends on runtime factors, it is inherently impossible to know them in advance of execution.

## 1.3 Objective of the Dissertation

In programming heterogeneous computing systems, there are many difficulties in performance tunings. To overcome the difficulties, a programming framework should automate some performance tunings and enables programmers to write programs without consideration of processors that are used to execute tasks. Figure 1.5 shows the overview of the programming framework proposed in this dissertation to overcome the difficulties. As shown in this figure, automatic tuning mechanisms work in compiler and runtime environment layers, and then automation of performance tunings can free programmers from labor-intensive performance tunings. Hence, the objective of this dissertation is to establish automatic performance tuning methods used in the programming framework that allows to develop a program without considering the underlying processors in a system. To achieve this objective, the programming framework has to appropriately assign tasks to processors, determine optimal execution parameters for a particular processor, and appropriately balance loads among accelerators. Therefore, this dissertation proposes the following three methods to automate these performance tunings and clarifies the effects of these methods through quantitative evaluations.

One proposed method is a domain-specific programming language to automate appropriate processor selection. In this language, programmers define *kernels* in a program that can be executed either on a CPU or on an accelerator. In a programming framework, the proposed method works in both compiler and runtime environment layers, as shown in Figure 1.5. In the compiler layer, the proposed method abstracts differences of processors to realize runtime processor selection. In the runtime environment layer, the proposed method automatically selects an appropriate processor for each kernel based on performance prediction. Thereby, the proposed language enables programmers to write a program without considering which processor is selected to execute kernels. Moreover, this runtime environment can select an appropriate processor not only for performance-aware computing but also for energy-aware computing that can optimize power efficiency of heterogeneous computing systems.

Another proposed method is use the features of the proposed programming language to achieve some automatic performance tunings. This proposed method works in the compiler layer shown in Figure 1.5 of the programming framework and applies some optimizations and tuning for automatically-generated programs at compiling. As a result, programmers do not need to examine various optimization techniques to improve the sustained performance

Figure 1.5: Performance tunings in programming frameworks.

of GPUs. This dissertation also achieves automatic tuning of execution parameters required for efficient use of GPUs.

The last proposed method is an online task scheduling method. If a heterogeneous computing system has multiple accelerators and if an application has the tasks that can be executed in parallel, called *parallel tasks*, load balancing is needed to simultaneously use those accelerators for parallel processing of the parallel tasks. For a parallel task whose execution time depends on its input data and varies dynamically, it is impossible to statically balance the loads among accelerators. Therefore, this dissertation proposes an online task scheduling method based on performance prediction to automate load balancing. The proposed scheduling method works in the runtime environment layer shown in Figure 1.5 to transparently realize automatic load balancing for an OpenCL program, and each parallel task in the OpenCL program is automatically assigned to an accelerator that can early complete the task. Then, this dissertation shows that the proposed scheduling method enables to efficiently use multiple accelerators.

## 1.4 Organization of the Dissertation

This dissertation is organized as follows.

Chapter 1 describes the background and the objective of this dissertation. In Chapter 1, the difficulties in programming for heterogeneous computing systems are pointed out: complicated and labor-intensive performance tunings are required to efficiently exploit accelerators of the system. Chapter 1 also describes the objective of this dissertation that is to establish automatic performance tuning methods used in a programming framework. The programming framework automatically performs the optimizations, tuning, and task assignment to alleviate the difficulties in programming heterogeneous computing systems. Thus, this dissertation proposes three useful methods to automate these performance tunings.

Chapter 2 proposes a domain-specific programming language for runtime processor selection. In Chapter 2, it is demonstrated that a processor is appropriately selected based on the performance prediction method in the following three chapters.

Chapter 3 describes automatic performance tuning methods for the domain-specific programming language proposed in Chapter 2. A program for a GPU must be sufficiently optimized for the architecture to fully exploit the computing capability of the accelerator. Hence, Chapter 3 proposes automatic optimizing methods to effectively use memory hierarchy in GPUs, and an execution parameter tuning method that determines the number of threads assigned to a processing core automatically.

Chapter 4 describes an online task scheduling method for a standard programming language, OpenCL, to automatically adjust loads among accelerators. Unlike the proposed domain-specific language discussed in Chapter 2, the latest standard programming languages such as OpenCL have high programming flexibility with few constraints. In these languages, there are difficulties in performance prediction and use of multiple accelerators. To automate load balancing among multiple accelerators, Chapter 4 proposes three methods: a highly-accurate performance prediction method, an analysis method to detect dependencies between parallel tasks, and an online task scheduling method.

Chapter 5 describes conclusions of this dissertation.

# **Chapter 2**

# A Domain-specific Language with Runtime Processor Selection

### 2.1 Introduction

To exploit the high computing performance of a heterogeneous computing system, programmers must appropriately use processors including CPUs and accelerators in the system. As accelerators such as GPUs especially have strengths and weaknesses about computation due to their application specific architectures, the sustained performance for a computation task strongly depends on the combination of the task and the available accelerator. Generally, accelerators work well only for tasks including massive data parallelism without complicated control flows. There is a case that the performance for a program is degraded by executing the program on accelerators. Hence, programmers must properly manage different kinds of processors to achieve a high performance.

The programming for heterogeneous computing systems of CPUs and GPUs, so-called *GPU programming*, is generally labor-intensive and error-prone. One of difficulties in GPU programming is how to determine which processor, either a CPU or a GPU, should be used for a given task. Even if a task is suitable for GPUs, finding an appropriate processor for the task is not easy. It is often difficult for a programmer and a compiler to ensure that a certain GPU in one PC can execute the task faster than its CPU. This is because the difference in sustained performance between a CPU and a GPU depends on individual tasks and information available only at runtime; such as the size of data processed by the task and the loop length in the task. As a result, the sustained performances of a CPU and a GPU drastically

change at runtime and are unpredictable even for expert programmers.

For energy-aware computing, GPUs can reduce the energy consumption of executing a program if GPUs considerably decrease the execution time. The energy efficiency also changes according to the sustained performance. Therefore, an appropriate processor selection mechanism is required to achieve high performance and/or energy-aware computing on a heterogeneous computing system.

CUDA [3] is currently the most popular programming language for GPU computing with NVIDIA GPUs. In CUDA, programmers define *tasks* as special functions, called CUDA kernels that are offloadable parts of a program to GPUs. A CUDA program needs at least one NVIDIA's GPU for execution, and other processors cannot execute a CUDA program. Hence, programmers must decide which processor executes a task and cannot change it at runtime. However, it is difficult to determine an appropriate processor for a task in advance of execution, because the appropriate processor may change at runtime. In some cases, it is needed to develop two programs of the same task for both a CPU and a GPU to select one of them at runtime, even though considerable efforts are needed to develop two versions for the task.

To alleviate burdens in programming, therefore, a programming language with runtime processor selection is useful. This language enables a programmer to describe a program without considering the processor to execute tasks because the program is automatically translated into a code for each processor. Then, each task is automatically assigned to an appropriate processor for performance-aware or energy-aware computing. Moreover, programmers can avoid unexpected performance degradation by inappropriate processor selection. Therefore, performance tuning by automatic processor selection is effective to alleviate one of difficulties in GPU programming.

In this chapter, a programming framework is proposed to realize runtime processor selection in a heterogeneous computing system. This framework consists of a domain-specific language and its runtime system. This chapter assumes a commodity personal computer (PC) as a heterogeneous computing system that has a CPU and a GPU. The design objective of the proposed programming language is as follows.

- To easily describe data-parallel processing that can be efficiently executed by accelerators such as GPUs.

- To easily predict an execution time for each accelerator.

• To select an appropriate processor based on performance prediction.

A lightweight runtime system is built to enable automatic processor selection considering the runtime information. Moreover, this chapter presents a metric to find the situation where one processor obviously outperforms another one. Then, this chapter shows that runtime processor selection can also improve energy efficiency.

#### 2.2 Related Work

# 2.2.1 Programming Environments for Heterogeneous Computing Systems

One research topic in software development for heterogeneous computing systems is how to abstract different kinds of processors such as CPUs and GPUs. A GPU generally prefers massive SIMD data parallelism. Hence, a GPU is often used for *stream processing*, which is modeled as a computation-intensive *kernel* for processing a long *data stream*. The stream processing can hide its memory access latency by making memory accesses highly predictable and overlapping data fetches with computations. Importance of the overlapping is growing more and more, due to the so-called memory wall problem [9]. The stream processing is suitable not only for GPUs but also for many other processors such as general-purpose processors [10] and heterogeneous multicore processors [11]; it will be a key technology to achieve high sustained performance with current and future computing systems.

Many researchers have demonstrated that GPUs can be seen as general-purpose stream processors [12]. Several high-level programming languages have been proposed to alleviate the programming efforts required to use the computing power of GPUs for stream processing applications [13, 14, 15, 16, 17]. However, they do not consider runtime processor selection for executing a given task in terms of the sustained performance and the energy efficiency.

Brook for GPU (BrookGPU) [13] is the first abstraction of GPUs for GPGPU programmers and is a popular programming tool that extends the standard C programming language to explicitly describe stream processing applications. BrookGPU provides a high-level programming language and its runtime backends to facilitate the development of GPGPU applications. Each of the runtime backends corresponds to a runtime environment supported by BrookGPU: CPU, OpenGL, and DirectX9. Using the Brook language, a programmer can explicitly write a kernel code. The Brook compiler is a source-to-source compiler that translates a Brook code into a standard C++ code. At the translation, a kernel code is translated into multiple codes respectively corresponding to runtime backends. When the executable file is launched, it first checks the environmental variable, BRT\_RUNTIME, to decide the runtime backend. Finally, all the kernels in an application program are executed using one of available processors called a *computing engine*.

There are also many programming tools that realize higher-level abstraction to facilitate GPU programming. RapidMind [14] and PeakStream [15] are both commercial software

Figure 2.1: The hardware architecture assumed in CUDA.

products to describe and execute multi-platform programs in a stream processing manner. In 2008, PGI has announced a commercial C/C++ compiler that defines additional compiler directives for generating CUDA codes from a standard C/C++ code [18]. HMPP also provides compiler directives to reduce the difficulties in the GPU programming [19]. However, they usually assume that a programmer or an application user statically determine the computing engine of every kernel in advance of the execution, even though appropriate processor selection clearly depends on various runtime behaviors and system configurations.

CUDA abstracts underlying hardware, and a programmer can describe a single program for NVIDIA GPUs even if the hardware configuration such as the number of processors in a GPU is different. Figure 2.1 shows the overview of the hardware architecture assumed in CUDA. In the execution model of CUDA, many threads are organized as arrays of threads and executed in parallel. A GPU is called a *device*, and one device has several *Multi-Processors (MPs)* that independently execute an array of threads. One MP consists of multiple *Stream Processors (SPs)*, each of which executes one thread. SPs in a MP cooperatively execute threads in an array in a Single-Instruction Multiple-Data (SIMD) [20] manner. If the branch targets of threads in an array are different, all the SPs in a MP execute both the paths.

Although Brook, CUDA, and the above libraries provide a high-level abstraction of

GPU programming, they do not consider that the difference in sustained performance between a CPU and a GPU depends on the information available only at runtime, such as the data sizes and GPUs installed in the system. Therefore, appropriate processor selection clearly depends on various runtime behaviors and system configurations [21]. It is often difficult even for expert programmers to determine the appropriate processor for a computation, because a programmer does not always know the performance difference when programming. As a result of inappropriate processor selection, use of GPUs may lead to the performance degradation rather than acceleration.

#### 2.2.2 Performance Model and Prediction

It is possible to improve performance by changing the processor to execute the kernel if the execution time of a kernel on one processor is obviously longer than that on another processor. Based on this idea, the kernel should be executed by the latter processor next time. Therefore, to select an appropriate processor, it is necessary to estimate the performances of two processors for each kernel.

There are some studies on performance evaluation and modeling of GPU computing applications. Since the GPU architectures are not fully disclosed, the GPU performance for various applications has been experimentally examined [22, 23, 24].

Govindaraju et al. investigated the details on a GPU memory hierarchy. Their memory model shows that the GPU's memory bandwidth depends on memory access patterns, and effective use of the two-dimensional cache memory can maximize the GPU performance [25]. Harrison et al. have assessed the execution time required for the data transfer between the main memory and the device memory [26]. As the time for the data transfer often becomes dominant especially in the case that a kernel has a low-arithmetic intensity, performance evaluation of the data transfer using different APIs is important to predict the total execution time of a GPGPU application. These experimental studies show that the performance prediction of GPGPU applications must consider styles of the implementations.

Ito et al. have proposed a model to estimate the execution time of a GPGPU application [27]. They assume that the GPU performance is always limited by its memory bandwidth, and hence the execution time of a kernel is in proportion to the size of data transferred between the GPU cores and the device memory. However, the actual memory bandwidth obviously depends on the memory access patterns. Therefore, He et al. have separately modeled sequential access performance and random access performance [28].

Buck et al. have presented BrookGPU with a simple performance model to analyze the performances of a CPU and a GPU [13]:

$$T_G = n(T_R + K_G), (2.1)$$

$$T_C = nK_C, (2.2)$$

where  $T_G$  and  $T_C$  are execution times of a GPU and a CPU, respectively,  $T_R$  is the time associated with downloading and reading back a single stream element,  $K_G$  and  $K_C$  are the times required to execute a kernel on a single element, and n is the number of elements in a data stream. It is obvious that the GPU will outperform the CPU only when

$$T_R < K_C - K_G. \tag{2.3}$$

This means, only if the performance gain by using a GPU exceeds the data transfer overhead, the GPU can outperform the CPU.

Transco et al. have reported a comprehensive experimental study of the performance comparison between a CPU and a GPU [29]. They investigated the execution times of BrookGPU kernels, changing kernel parameters such as the computation intensity, the data size and the data format. Their results clearly indicate that the GPU's superiority in performance depends on several parameters determined at runtime.

As the BrookGPU language can describe only stream kernels, it is relatively easy to model the performance of each kernel. However, it is difficult to automatically generate the performance model of arbitrary CUDA codes [30] because of its high programming flexibility. Therefore, one idea to achieve runtime processor selection is to limit the programming flexibility so that a runtime system can easily predict the performance. Since GPUs basically are suitable for stream processing, the flexibility-limited programming language can still describe many significant GPU applications even if it can describe only kernels of stream processing.

In addition to performance improvement, energy-aware computing also has become more and more important not only in mobile systems but also in *high-performance computing* (HPC) systems. Göddeke et al. have reported that use of even low-end and out of date GPUs leads to improvements in both performance- and power-related metrics of a GPU-accelerated cluster system for FEM applications [31]. Use of GPUs generally increases the power consumption, however, it does not always increase the performance. As a result,

it may lead to the increase in energy consumption for the applications, which cannot be efficiently executed by GPUs. Accordingly, runtime performance prediction is needed to achieve appropriate processor selection in terms of energy efficiency; GPUs should be used only if its energy consumption of executing a program is substantially small because of the performance gain by GPUs.

# 2.3 A Domain-specific Language with Runtime Processor Selection

#### 2.3.1 Overview

In this section, a programming framework named *Stream Programming with Runtime Auto-Tuning* (SPRAT) [32] is proposed to realize runtime processor selection. This framework consists of a domain-specific language to describe data-parallel processing, called the *SPRAT language*, and the SPRAT runtime environment for dynamic selection of an appropriate processor. As with BrookGPU [13], the SPRAT compiler translates a SPRAT code into multiple codes, each of which is corresponding to one processor. The processor for executing each kernel is called a *computing engine* in SPRAT. According to the runtime behaviors that are not available for a programmer and a compiler, the SPRAT runtime environment dynamically switches the computing engine so as to minimize the execution time or the energy consumption; a GPU is used as a computing engine only if it can accelerate the kernel execution or reduce the energy consumption.

Without any preknowledge, it is difficult to automatically predict the execution time of an arbitrary code. To achieve runtime performance prediction of user-defined functions, hence, the SPRAT language provides special functions, named *kernel functions*, in which a programmer can write only stream processing kernels. As a kernel function is applied to every stream element, the execution time increases linearly with the number of stream elements. When a stream is given, therefore, the SPRAT runtime environment can estimate the execution time of each kernel function with a simple performance prediction model of linear approximation.

## 2.3.2 Stream Programming language with Runtime Auto-Tuning (SPRAT)

The SPRAT language is an extension of the standard C language incorporating some special keywords for description of stream processing tasks. In a stream processing task, a *stream* is a collection of data processed by a *kernel*. A stream is declared with the stream keyword and angle-bracket syntax. A kernel function, which operates on individual stream elements, is specified by the kernel qualifier. The syntax of the SPRAT language itself is similar to the conventional stream programming languages such as BrookGPU [13].

Figure 2.2 illustrates how a SPRAT code is converted into an executable file. A SPRAT

Figure 2.2: The compiling flow of a SPRAT program.

code written by a programmer is first translated into multiple codes: a standard C++ code for a CPU and a CUDA code for a GPU. Then, a programmer can manually optimize the automatically-generated codes if needed. Finally, those codes are respectively compiled and then linked with the SPRAT runtime library to generate an executable file.

The details on streams and kernels are described as follows.

#### **Streams**

In the SPRAT language, a variable declared with the stream keyword is used as a container of stream data. The number and the variable type of stream elements are specified in the stream variable declaration.

Since stream elements are directly accessible only within a kernel function, there are built-in functions to manage stream data. For example, streamRead and streamWrite are used for the data transfer between a standard C array and a stream. The former copies

Listing 2.1: A sample code of a reference stream.

```

1 stream<float>& ref = strm[i][j](w,h);

```

Listing 2.2: An equivalent code for the kernel code.

each array element to its corresponding stream element. The latter copies each stream element onto its corresponding array element.

There are four kinds of qualifiers to specify the access attributes of a stream: in, out, inout, and gather. A stream specified by the in keyword permits sequential read-only accesses. A stream with the out keyword permits sequential write-only accesses. A stream specified by inout is both readable and writable. An element in a gather stream can be read using an array index operator to be mentioned later.

In addition, a stream reference to a part of stream elements can be declared as shown in Listing 2.1. Here, a stream reference ref represents the domain of a 2-dimensional stream strm whose left-upper corner position and size are specified by [i][j] and (w,h), respectively. Note that ref and strm share the same memory area of w×h stream elements.

#### **Kernels**

A kernel, which operates on each stream element, is described by a special function specified by the kernel keyword. A programmer cannot permute the sequence of stream elements; they may independently be processed in parallel.

A kernel function with the map qualifier takes one or more output streams specified by the out or inout keyword. The kernel execution is a data-parallel task that logically computes all the output stream elements. For example, the <code>saxpy</code> function in Listing 2.3 is implicitly translated by the SPRAT compiler to the multiple codes, each of which has the same meaning of the nesting loops shown in Listing 2.2. In this listing, N and M indicate the width and height of streams.

Every input stream element is corresponding to one of elements in an output stream based on the position in the input stream by default. However, a stream specified by the gather qualifier can be accessed using an array index operator. A gather stream element

Figure 2.3: The coordinate in gather access.

is accessed using the array index that indicates the relative position from the corresponding output stream element. For example, strm[0][0] of a 2-dimensional gather stream denotes a stream element whose position is the same as that of the calculated output stream element; strm[-1][0], strm[1][0], strm[0][-1], and strm[0][1] indicate the four neighboring elements of strm[0][0], as shown in Figure 2.3. As a stream processing task often accesses the neighboring stream elements, the array index operator indicates the relative position from the corresponding output stream element. If a kernel function must always refer to the i-th element of stream s, it can be expressed using a special index operator, s[[i]].

Listing 2.3 shows a sample code written in the SPRAT language. In the code, a kernel function saxpy is called with a scalar value pi, two input streams sX and sY, and an output stream sZ. Here, each of sX, sY, and sZ contains the same number of stream elements.

Listing 2.3: A sample code of saxpy written in the SPRAT language.

```

kernel map saxpy(

float a,

2

3

4

5

6

7

8

9

in stream<float> x,

in stream<float> y

out stream<float> z)

{

z = a * x + y;

return;

}

10

11

int main(int argc, char** argv)

12

13

14

15

16

17

18

19

20

21

22

23

init_array( x, y);

streamRead(sX, x);

streamRead(sY, y);

saxpy(pi, sX, sY, sZ);

streamWrite(sZ, z);

print_array(z);

return 0;

```

Stream elements at the same position in different streams are corresponding to each other. Every element of sX is multiplied by pi, and then is added to its corresponding element of sY. The calculation result is written to the corresponding element of sZ. Since a stream element is accessible only within a kernel function, elements of arrays x and y are copied onto sX and sY using streamRead function. Similarly, elements of sZ are copied onto z using streamWrite function.

#### 2.3.3 Performance Prediction and Processor Selection

To select an appropriate processor, the SPRAT runtime environment profiles the execution times of kernels, and builds linear prediction models for each processor using profile data. The runtime environment automatically selects the processor that can execute a kernel in the minimum execution time.

#### **Performance Modeling of Kernels**

If a programmer directly writes a GPU computing code using graphics APIs and/or CUDA, styles of the implementations should be considered in performance prediction because they considerably affect the performance [24, 25, 26]. As SPRAT sacrifices the flexibility of programming styles to some extent, a kernel code written in the SPRAT language is automatically translated into multiple codes corresponding to a CPU and a GPU. Therefore, by

taking into account the translation rules, it is needed to consider only one style of the implementation for performance prediction, which becomes tractable in performance prediction.

In a stream processing task, an identical kernel computation is performed to produce each element in an output stream. Hence, the execution time of a kernel almost linearly increases with the number of output stream elements. To restrain the runtime overhead, a simple model is preferable for runtime performance prediction. Therefore, the SPRAT framework uses a simple linear performance model to estimate the execution time of a kernel from the number of elements in an output stream:

$$T_p(k_i) = \frac{D(k)}{B_p(k_i)} + S_p(k_i),$$

(2.4)

where  $T_p(k_i)$  is the execution time required by the processor p to execute kernel  $k_i$ ,  $D(k_i)$  is the number of output stream elements,  $B_p(k_i)$  is the sustained throughput of the processor p for kernel  $k_i$ , and  $S_p(k_i)$  is the startup time required by the processor p to launch kernel  $k_i$ .

Similarly, the data transfer time also increases with the size of the transferred stream data [23]:

$$T_{p \to q} = \frac{D_{p \to q}}{B_{p \to q}} + S_{p \to q},\tag{2.5}$$

where  $T_{p\to q}$ ,  $D_{p\to q}$ ,  $B_{p\to q}$ , and  $S_{p\to q}$  are the total time, the data size, the sustained bandwidth, and the startup time of the data transfer from the processor p to the processor q, respectively.

In general, the linear performance model presented above can precisely estimate the execution time of a kernel on a GPU. However, if the execution times are profiled for only the streams whose sizes are small, it may overestimate the CPU performance without considering the effects of cache spilling of large streams. One possible approach is to use additional performance parameters,  $B'_{p,k_i}$  and  $S'_{p,k_i}$ , to estimate the CPU performance when the kernel is called with a large stream whose size  $D_{k_i}$  exceeds the cache capacity. Accordingly, the modified performance model estimates the execution time required by CPU to execute kernel  $k_i$  by

$$T_{C,k_i} = \begin{cases} \frac{D_{k_i}}{B_{C,k_i}} + S_{C,k_i} & \text{if } D_{k_i} < D_{\$} \\ \frac{D_{k_i}}{B'_{C,k_i}} + S'_{C,k_i} & \text{otherwise} \end{cases},$$

(2.6)

where  $D_{\$}$  is the size of the last level cache. The SPRAT runtime environment can get the value of  $D_{\$}$  by using system query API.

#### **Energy Consumption Modeling of Kernels**

In addition to performance parameters, power consumption parameters are also required for energy-aware computing. In this section, it is assumed that the power consumption is independent from kernels and depends only on the processor that executes kernels. Then, power consumption parameters can be regarded as system-specific parameters and need to be measured once for a system. The validity of this assumption is experimentally discussed later in Section 2.4.

Let  $P_p$  be the wattage when using the processor p as a computing engine. Similarly,  $P_{p\to q}$  denotes the wattage for the data transfer from processor p to processor q. This allows even a simple watt meter to measure the wattages such as  $P_p$  by running a test kernel that executes saxpy on the GPU and the CPU for a long time; this does not need an expensive measuring instrument.  $P_{p\to q}$  is also measured by transferring data from the memory of processor p to the memory of processor p for a long time.

Using these coefficients such as  $P_p$  and  $P_{p\to q}$ , power consumption of executing kernels and data transfer can be indicated by

$$E_p(k_i) = P_p \cdot T_p(k_i) = P_p \left\{ \frac{D(k_i)}{B_p(k_i)} + S_p(k_i) \right\},$$

(2.7)

and

$$E_{p\to q} = P_{p\to q} \cdot T_{p\to q} = P_{p\to q} \left\{ \frac{D_{p\to q}}{B_{p\to q}} + S_{p\to q} \right\}, \tag{2.8}$$

where  $E_p(k_i)$  and  $E_{p\to q}$  are the amount of energy consumption of executing the kernel  $k_i$  on the processor p and data transfer p to q, respectively. Moreover, to accurately estimate the performance of a CPU with cache memory, the modified prediction model estimates the energy consumption of the CPU executing kernel  $k_i$  by

$$E_{C}(k_{i}) = P_{C}(k_{i}) \cdot T_{C}(k_{i}) = \begin{cases} P_{C}(k_{i}) \left( \frac{D_{k_{i}}}{B_{C,k_{i}}} + S_{C,k_{i}} \right) & \text{if } D_{k_{i}} < D_{\$} \\ P_{C}(k_{i}) \left( \frac{D_{k_{i}}}{B_{C,k_{i}}'} + S_{C,k_{i}}' \right) & \text{otherwise.} \end{cases}, \tag{2.9}$$

#### **Measuring Coefficients for Prediction**

Performance prediction by SPRAT requires all the parameters in advance. Among the parameters, the parameters involved in the execution time of the kernel i such as  $B(k_i)$  and

$S(k_i)$  must be obtained for individual kernels; the others are system-specific parameters and are measured only once for a computing system. For measuring those performance parameters, an application user needs to run the program several times in advance. For example, the performance parameters are obtained by the first 10 executions; five times for the CPU parameters and the others for the GPU ones. Appropriate data sizes are properly given by the user to improve the accuracy of the prediction. The parameters of executing the kernel are measured and are automatically stored in a parameter database.

#### **Strategies of Processor Selection**

A CPU can access only the data on the main memory, while a GPU can access only on the device memory. When a computing engine is switched, the stream data to be accessed by the kernel function have to be transferred to the memory space of the new processor. Since the data transfer induces a considerable overhead, the dynamic switching has to be carefully decided by taking into account the trade-off between the data transfer overhead and the performance gain by switching.

Similar to Equation (2.3), one may claim that the appropriate processor can be found by comparing the execution time of a CPU to that of a GPU. That is, in the case where a CPU is currently selected as a computing engine, a computing engine for executing kernel  $k_i$  should be switched to a GPU only if the following condition is met.

$$T_C(k_i) > T_G(k_i) + T_{C \to G},$$

(2.10)

where processors C and G denote the CPU and the GPU, respectively.

However,  $T_{C \to G}$  is generally larger than  $T_C(k_i)$  and  $T_G(k_i)$  especially if  $k_i$  is a user-defined simple kernel function. Even if a GPU is much faster than a CPU and can reduce the total execution time, the processor will not be switched from the CPU to the GPU. Accordingly, Equation (2.10) does not always result in appropriate processor selection. Suppose that  $T_C(k_i)$  is greater than  $T_G(k_i)$  but less than  $T_G(k_i) + T_{C \to G}$ . Then, the GPU can reduce the total execution time by almost  $\sum_{i=1}^N \{T_C(k_i) - T_G(k_i)\}$ , if the processor is switched from the CPU to the GPU and then kernel  $k_i$  is called N times. Accordingly, if N satisfies the

following condition, a processor should be switched from the CPU to the GPU.

$$T_{C \to G} < \sum_{i=1}^{N} \{ T_C(k_i) - T_G(k_i) \}.$$

(2.11)

In many cases, however, it is difficult to obtain the actual stream size  $D(k_i)$  used for estimating  $T_p(k_i)$  and  $T_{p\to q}$  in advance of the kernel call.

To solve this problem, the *accumulated time difference* is introduced to SPRAT for appropriate processor selection. In the case where processor p is used as a computing engine, the accumulated time difference of processor q is updated at every kernel call as follows.

$$\Delta T_q := \max\{\Delta T_q + (T_p(k_i) - T_q(k_i)), 0\}. \tag{2.12}$$

Hence,  $\Delta T_q$  indicates how much the execution time is shorten if q is used as a computing engine. SPRAT switches a computing engine from p to q if the following condition is met.

$$T_{p \to q} < \Delta T_q. \tag{2.13}$$

When the computing engine is switched from p to q, the accumulated time difference of each processor is cleared to 0,

$$\Delta T_n := 0, \tag{2.14}$$

and

$$\Delta T_a := 0. (2.15)$$

In the case of energy-aware computing, the *accumulated energy difference* is also introduced to SPRAT. When the processor q is not used as a computing engine, the accumulated energy difference of processor q is updated at every kernel call as follows.

$$\Delta E_q := \max\{\Delta E_q + (E_p(k_i) - E_q(k_i)), 0\}. \tag{2.16}$$

Hence,  $\Delta E_q$  indicates how much energy is saved if q is used as a computing engine and is used instead of  $\Delta T_q$  in energy-aware processor selection.

#### A DOMAIN-SPECIFIC LANGUAGE WITH RUNTIME PROCESSOR SELECTION

These metrics assume iterative computations and realize a lightweight runtime environment that can select an appropriate processor based on the trend of stream sizes in the past. Thereby, these metrics speculatively customize an application program to common stream sizes in the future kernel calls. Although this needs the extra execution time or energy of  $T_{p\to q}$  or  $E_{p\to q}$  until switching the computing engine to the other processor, it will be negligible in many cases where a sequence of some kernels is periodically invoked many times.

# 2.4 Evaluation

### 2.4.1 Experimental Setup

This section shows the evaluation results to examine the performance of the proposed runtime processor selection for performance-aware and energy-aware computing. All of the evaluation results are obtained using a Linux PC equipped with Intel Core 2 Quad (C2Q) Q6600 Processor running at 2.4GHz, DDR2 4GB main memory, and one of GPUs listed in Table 2.1. In the table, # SPs indicates the number of streaming processors in the GPU. Mem, CFreq, MFreq, and BW indicate the memory capacity, the core clock frequency, the memory clock frequency, and the peak memory bandwidth, respectively. GFGTX280 means NVIDIA GeForce GTX280. GF88GTX is the abbreviation of NVIDIA GeForce 8800 GTX, and the other GPU models are also abbreviated in the same way.

The Linux kernel version is 2.6.18 (CentOS 5 x86\_64) and C++ compiler that compiles the SPRAT runtime environment and codes for CPUs automatically-generated by the SPRAT compiler is gcc-4.2.1 with "-O3" options. The NVIDIA graphics driver version 173.14, the CUDA version 1.1, and CUDA compiler version 1.1 V0.2.1221 are used. At every execution of a SPRAT program, a CPU is initially selected as the computing engine for kernel execution, and then the computing engine is switched according to runtime performance prediction.

#### 2.4.2 Evaluation of Performance-aware Processor Selection

To clarify the effectiveness of the SPRAT framework for a programmer who does not have knowledge of GPU programming, the computational fluid dynamics (CFD) simulation code

| Processor         | Abbreviated | # SPs | Mem. | CFreq. | MFreq. | BW.    |

|-------------------|-------------|-------|------|--------|--------|--------|

| Name              | Name        |       | [MB] | [MHz]  | [MHz]  | [GB/s] |

| GeForce GTX 280   | GFGTX28     | 240   | 1024 | 1296   | 1107   | 141.7  |

| GeForce 8800 GTX  | GF88GTX     | 128   | 768  | 1350   | 900    | 86.4   |

| GeForce 8800 GT   | GF88GT      | 112   | 512  | 1500   | 900    | 57.6   |

| GeForce 8600 GTS  | GF86GTS     | 32    | 256  | 1450   | 1000   | 32.0   |

| Core 2 Quad Q6600 | C2Q         |       | 4096 | 2400   | 800    | 12.8   |

Table 2.1: Specifications of GPUs used for evaluation.

Figure 2.4: Speedup ratio of the CFD simulation.

shown in Listing 2.4 is used for the following evaluation. In this evaluation, the CFD program calculates 100 simulation steps of the 2-dimensional cavity flow using the fractional step method [33]. The Jacobi iteration method is used for the pressure calculation. In the case where the pressure calculation is performed on GPU, the error is transferred from GPU to CPU to check the convergence. In this evaluation, a convergence difference is calculated, but it is not used to exit the loop of pressure calculation.

To measure prediction parameters for each processor, the CFD program is executed for every kernel with the grid sizes of  $32 \times 32$ ,  $64 \times 64$ ,  $128 \times 128$ ,  $256 \times 256$ , and  $512 \times 512$ . Moreover, the additional prediction parameters of CPU for large streams are measured to consider the capacity misses with the grid sizes of  $1024 \times 1024$ ,  $1536 \times 1536$ ,  $2048 \times 2048$ ,  $2560 \times 2560$  and  $3072 \times 3072$ .

Figure 2.4 shows the speedup ratio of three GPUs measured with changing the data size. In Figure 2.4, the performance is obtained by counting the number of grid points per second, and then the speedup ratio of each processor to CPU is computed.

For the CFD code, all the GPUs significantly outperform C2Q in large grid sizes. However, in very small grid sizes, GPUs cannot outperform C2Q because there are overheads for executing kernels on GPUs such as data transfers. Moreover, the cache memories of C2Q provide a higher memory bandwidth than those of GPUs. Hence the performance is degraded if the computing engine is fixed to GPUs when the grid size is very small.

If one processor is much faster than the other, SPRAT can easily select the appropriate processor. In the evaluation results shown in Figure 2.4, all the GPUs are almost always used as a computing engine, and C2Q is used only when the grid size is approximately equal to or less than  $64 \times 64$ . The evaluation results clarify that even a middle-range GPU, GF86GTS, has a possibility to achieve a high performance, if the application is well-suited for GPU computing. In this case, SPRAT enables programmers who do not have knowledge of GPU computing to appropriately exploit the computing power of a middle-range GPU without risks of performance degradation.

In most cases, the performance using runtime processor selection is less than the performance especially when a computing engine is fixed to an appropriate processor. This difference in performance appears when the appropriate processor is a GPU. This is because a CPU is selected as an initial computing engine, and there is a certain overhead of data transfers and kernel launch to switch the computing engine from a CPU to a GPU. However, it would be negligible if the initial overhead becomes small compared to the total execution time.

# 2.4.3 Evaluation of Energy-aware Processor Selection

To realize runtime processor selection for energy-aware computing, the power consumption parameters required to predict energy consumptions are measured in advance. Table 2.2 shows the power consumption of each system configuration under full load. The power consumption is measured with HIOKI HITESTER 3334 [34] while the saxpy function in Listing 2.3 is iteratively running on either a CPU or a GPU.

Table 2.2: Power consumption of each system configuration.

| System Configuration | $P_G[\mathbf{W}]$ | $P_C$ [W] | $P_{C \to G}$ [W] | $P_{G \to C}$ [W] |

|----------------------|-------------------|-----------|-------------------|-------------------|

| C2Q + GF88GTX        | 251.4             | 204.9     | 214.6             | 213.2             |

| C2Q + GFGTX28        | 305.3             | 212.7     | 210.3             | 209.2             |